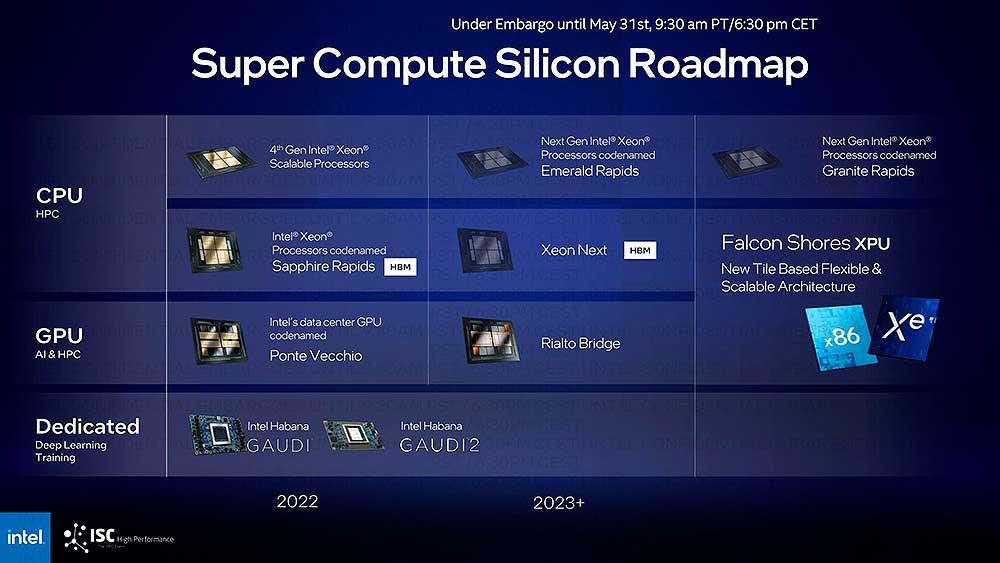

Nach der offiziellen Vorstellung der NVIDIA H100 mit all seinen extrem erstaunlichen Neuigkeiten, Intel kommt jetzt und kommt mit einer Vorschau auf die nächste Zukunft und einer Vorschau auf das, was in der Welt von KI und HPC kommen wird, auf den Tisch. Rialto-Brücke wird der definierende und letzte Punkt von GPUs sein, wie wir sie heute kennen, da die Zukunft darin liegt XPU unter Falcon Shores. In der Zwischenzeit sind diese neuen GPUs ein großer Schritt für Pat Gelsinger, um sich eine bedeutende Nische in der Schlüsselindustrie zu schaffen, die heute die Welt dominiert.

Was das Unternehmen präsentiert, ohne Leistung dazwischen, stellt den nächsten Evolutionsschritt gegenüber Ponte Vecchio dar, GPUs, die als solche noch nicht den Markt erreicht haben und stattdessen bereits Nachfolger haben. Was enthüllt wird, konzentriert sich auf 6 Schlüsselaspekte, die wir aufschlüsseln werden, obwohl die Aussagen erwartungsgemäß kurz sind.

Intel Rialto Bridge, die beste GPU, die bisher entwickelt wurde

Es gibt hier keine großen Neuigkeiten und einige davon sind zu erwarten, wir könnten perfekt sagen, dass die Rialtobrücke eine logische Weiterentwicklung der Ponte Vecchio ist, die einer sehr ähnlichen Struktur folgt, und wir hätten Recht. Das erste, was wir berücksichtigen müssen, ist die IDM 2.0-Strategie von Intel, die den Ponte Vecchio hat GPU als seine Bastion ein viel fortgeschritteneres Niveau erreichen wird und dass seine Hauptattraktion die Knotenänderungen in seinen verschiedenen Teilen sein werden.

Sie wurden nicht als solche spezifiziert, aber es gibt einige Gerüchte, dass Link Tiles unter TSMC auf 5 nm gehen könnten, GPU-Dies auf N4 und Caches und andere Teile wie Passive Die Stiffeners mit Intel 4.

Auf der anderen Seite eliminieren die gezeigten Folien einen der zuvor diskutierten Faktoren, da sie Intels RAMBO-Cache merkwürdigerweise nicht zeigen. Dies könnte darauf hindeuten, dass Intel es in die GPU-Kacheln aufnehmen und dadurch komplexere Chips erstellen wird, die mit ihm ankommen könnten Intel 4 Herstellungsknoten und lassen Sie TSMC in diesem Teil des Spiels beiseite.

Die Tatsache der Verwendung HBM3 Auch Speicher wird gemunkelt, der eine höhere Bandbreite geben würde und Intel dazu zwingt, seinen zu aktualisieren Xe-Link die Architektur . Es muss verstanden werden, dass jede beschleunigende GPU dieses Typs die Speicherbandbreite als Hauptbeschränkung hat, die Leistung ist proportional dazu, weshalb Intel mehr FLOPS und GT/s ankündigt, ohne weitere Erklärungen zu geben.

Lassen Sie uns jedoch zu anderen ebenso wichtigen Aufgaben mit der Rialtobrücke springen.

OAM 2.0, der Verbrauch und die Steigerung von Kernen

Der Sockeltyp, den Intel für die Rialtobrücke verwenden wird, wird sein OAM 2.0 , was eine Überraschung ist, da wir nichts darüber wussten und nach dem Gesagten auch eine brutale Zahl in Bezug auf Kapazitäten und Verbrauch vermuten lassen, da wir mit seiner ersten Version mindestens 700 Watt überschritten haben 800 Watt in diesem zweiten.

Diese Erhöhung soll wirklich mehr Effizienz erreichen, denn wenn wir berücksichtigen, dass Ponte Vecchio 128 EUs umfasst, reicht die Rialtobrücke bis zu 160 Kerne Xe unter seinem Gürtel eine Steigerung von 25%, was angesichts der Steigerung von 100 Watt tatsächlich zu einer höheren Effizienz führt.

Was die Leistung selbst betrifft, versichert Intel, dass wir sehen werden, wie sie abhebt 30% , was angesichts der Zahlen, die wir für Kerne vorgelegt haben, nicht beeindruckend ist, aber es ist allgemein ein Sprung nach vorne, da die endgültigen Frequenzen nicht angezeigt werden.

Schließlich und bevor wir über die Zukunft dieser Technologie als solche sprechen, hat Intel das Datum von festgelegt Sampling 2023 für Rialto Bridge ohne Angabe eines Quartals, Zahlen, die denen von NVIDIA mit H100 und seinen Grace-Servern sehr ähnlich sind, wo hier die von Huang sie einen gewissen Vorteil haben. Und es ist so, dass das Ziel von Intel klar ist, wenn wir uns die von ihm bereitgestellte Roadmap ansehen: 2023 wird das Jahr sein, in dem der neue Xeon und die Rialto-Brücke eintreffen und 2024 oder 2025 den Sprung zu machen Falkenküste , die Architektur, die beides in einem neuen Konzept namens vereinen soll XPU .

Die Zukunft sind Falcon Shores, die XPUs, die den Markt revolutionieren werden

Falcon Shores wird die Implementierung mit Tiles auf flexible und skalierbare Weise ermöglichen, eine Wendung zu dem, was wir mit dem gesehen haben NVIDIA Grace-SUPERCHIP wo mit EMIB und Foveros 3D Intel den Sprung zu einem einzigen modularen Produkt macht, das durch einen einzigen Sockel alle Arten von Produkten für den Verbraucher haben kann. Von GPUs, CPUs bis hin zu einer Mischung aus beidem wird dieses XPU-Konzept eindeutig das vorherrschende in der Branche sein, so dass wir die Möglichkeit nicht ausschließen, einige Teile eines FPGA zu integrieren.

Intel gibt mehr oder weniger interessante Details, da es heißt, dass mit Falcon Shores die Leistung pro Watt um das bis zu 5-fache gesteigert wird, die Dichte pro x86-Sockel um 5 mal und die Speicherkapazität und S/W im gleichen Wert, ein Konzept, das später viel einfacher und vor allem billiger auf den PC importiert werden wird, wo wir zum Glück nicht so viele Änderungen als solche haben werden (niedrigerer Preis).

Und es ist, dass wir von einem sehr anständigen beginnen CPU und GPU-Basis, die nur durch modulare Verpackungs- und Verbindungstechnologien verbessert wird, wodurch Intel direkt zur MCM-Architektur übergeht AMD wird mit Zen 4 und seinen iGPUs zu tun haben.