Vor fast einem Jahr Intel enthüllte eine der relevantesten Technologien für dieses Jahrzehnt und damit eine Architektur, die alle von der Herangehensweise und Implementierung des Blues überraschte. Diese Architektur ist SeeFeld , das sich seit Jahrzehnten in der Entwicklung befindet und über das wir nachdenken dürfen, aber was ist das und warum ist es so revolutionär?

Der Ansatz, den Intel für diese Architektur und SoC gewählt hat, mag kompliziert erscheinen, aber die Realität sieht genauso aus ARM hat sich mehr oder weniger anständig auf dem Server- und Desktop-Markt behauptet, jetzt wird Intel versuchen, den Markt für Smartphones, Fernseher und allgemein den sogenannten anzugreifen IoT .

LakeField ist kein Schritt, sondern ein Sprung in die Zukunft aufgrund dessen, was es darstellt und wie es gestaltet ist, was gleichzeitig das Interessanteste an der Architektur ist.

Die 3D-Implementierung von Intel LakeField erreicht die Chips der Zukunft

Lassen Sie uns die Hauptkarten auf den Eingangstisch legen, um die Art der Technologie zu verstehen, auf die wir uns beziehen, und die Auflistung dieser Karten ist einfacher zu verstehen:

- Wir stehen vor einem mobiler SoC.

- Sehr geringer Verbrauch ( 2 mW ).

- Intels erste echte Multi-Core-Architektur.

- Vorname Penta-Kern in seiner Geschichte.

- Der erste Chip des Unternehmens basiert auf dem big.LITTLE Konzept.

- Integrierte Gen 11 iGPU .

- Foveros-Technologie mit 3D-Chip-Verpackung.

- Unterstützung für LPDDR4X .

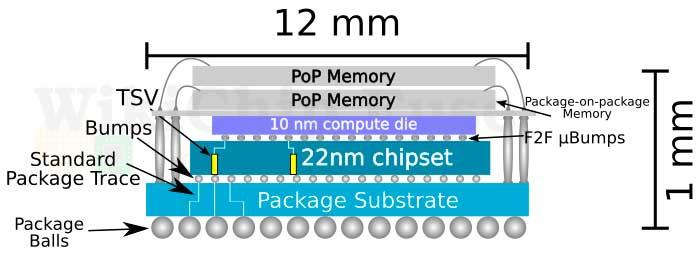

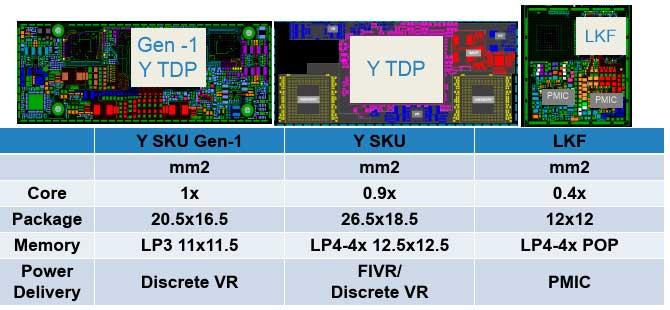

- Es wird nur besetzen 12 x 12 mm mit 1mm Höhe.

Viele Konzepte, viel Innovation und vor allem jahrelange Entwicklung, die die Säule der Prozessoren der neuen Generation bilden werden, nicht nur von Intel, sondern auch von AMD und der Rest der Unternehmen, die wettbewerbsfähig sein wollen. Der gesamte Sektor konzentriert sich auf das sogenannte 3D-Paket. Machen wir uns nichts vor, es ist die Zukunft und bald wird es die Gegenwart sein, aber um es zu verstehen, ist es notwendig zu verstehen, wie LakeField hergestellt wird.

3D-Stapelung, das Fundament der neuen Werkzeuggeneration

Es ist nicht schwer, das Konzept von 3D-Stempeln zu verstehen. Es handelt sich um Chips, die vertikal miteinander verbunden sind und über verschiedene Technologien verfügen, über die wir bereits gesprochen haben, z EMIB, Foveros oder Co-EMIB über ODI.

Bei LakeField war Intel ebenso ehrgeizig wie intelligent. Das Substrat (Matrix) wurde für alle Funktionen verwendet, die Intel als "Low Power" bezeichnet. Dies umfasst die USB-C 3.0-Schnittstelle, einige Eingangs- und Ausgangsbusse mit geringerer Leistung und insbesondere die PCIe Gen 3-Schnittstelle.

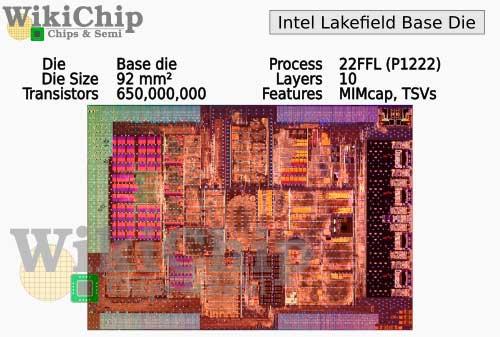

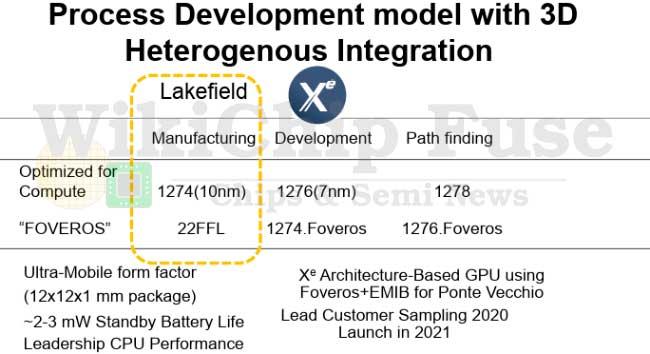

Als gute Basis ist es größer als die endgültige Größe des Chips und rühmt sich 92 mm2 unter dem 22-nm-FFL-Prozess, auch 22FFL genannt, der zwar aufgrund seiner Nomenklatur nicht so aussieht, aber tatsächlich ein sehr spezifischer Prozess für diese Art von Produkten ist, die auf 14 nm basieren, aber für mobile SoCs optimiert sind.

Daher werden die Transistoren bei 14 nm aufgezeichnet und erleichtern dadurch die Effizienz der gesamten Matrix. Es ist billig, verfügt über verbesserte Funktionen, die für diese Art von Produkt spezifisch sind, und es hat weniger Schichten als ein normaler Chip. Daher kann Intel seine neuen 10 nm und die nächsten 7 nm, bei denen die Kosten immer noch sehr hoch sind, am besten sparen.

Der Würfel ist der fortschrittlichste, den Intel bisher entwickelt hat

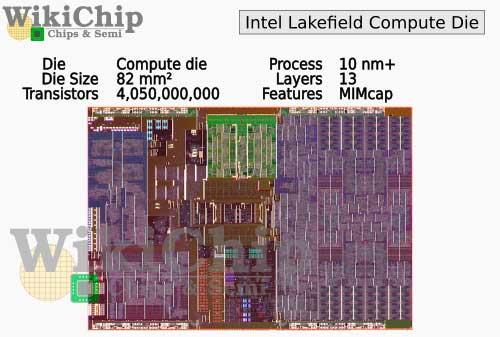

Angesichts seiner Basis werden wir uns mit dem Chip selbst vorstellen, wo alle Vorteile und Neuheiten dieser Architektur und dieses Chips liegen. Wir sprechen von einem Chip von nur 82 mm2 mit mehr als 4 Milliarden Transistoren, was zeigt, dass die Dichte absolut brutal ist und bisher nicht gesehen wurde.

Dies hat seine Erklärung und es ist, dass LakeField unter dem neuen ankommen wird 10nm+ von Intel, dh der zweiten Generation seines neuen lithografischen Verfahrens, das die Frequenz im Vergleich zur zweiten Version erheblich erhöht und die endgültige Dichte ein wenig verbessert. Hier muss betont werden, dass anscheinend 37% des Chips für die iGPU ausgegeben werden, was die Anstrengungen zeigt, die Intel mit Gen 12 unternehmen muss, um integrierte Grafikkarten leistungsfähiger und mit weniger endgültiger Fläche in einem Chip zu machen.

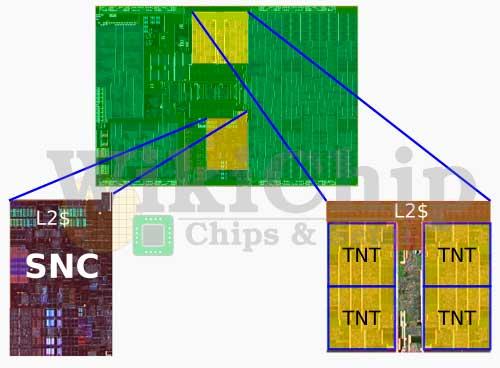

Für die Kerne selbst finden wir vier, die auf der Tremont-Architektur basieren, und eine einzige Sunny Cove, in der Intel Hyper Threading nicht aktiviert hat. Dies wurde auf diese Weise getan, um die Verteilung von Aufgaben in den Betriebssystemen zu erleichtern, da es den Entwicklern anscheinend einige Zeit dauern wird, bis diese Technologie die erwartete Leistung erbringt.

Der Vorteil hierbei ist andererseits, dass ein Tremont-Kern mit der gleichen Frequenz wie eine Sunny Cove bis zu 70% seiner Leistung erzielt, jedoch mit einem unendlich geringeren Verbrauch.

Dies erfordert, dass Workloads für die größten Kerne in Bursts eintreffen, während Hintergrundprozesse von den 4 Tremont-Kernen verwaltet werden, wodurch viel Energie gespart wird.

Schließlich wird geschätzt, dass alle vier Tremont-Kerne ähnlich groß sind wie der Sunny Cove-Kern, einschließlich ihrer Caches und AVX-512-Anweisungen (standardmäßig deaktiviert), damit wir eine Vorstellung davon bekommen, welches Potenzial zukünftige Chips haben könnten. fast zum gleichen Bereich.

Foveros

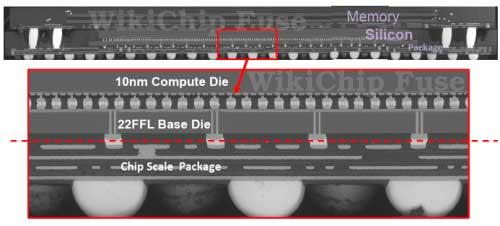

Wir haben bereits lange und intensiv über diese Technologie und ihre Schwestern gesprochen, daher werden wir den theoretischen Teil überspringen, um kurz zu kommentieren, wie Intel seine Chips vertikal anordnen will. Wir werden zwei Hauptschichten plus die haben LPDDR4X RAM Erinnerung Chips, was beeindruckend ist.

Die Matrix wird "von Angesicht zu Angesicht" mit dem 22-nm-LFF-Substrat unter Verwendung von 50-um-Mikrobuckeln verbunden, und dies wiederum mit dem Hauptpaket. Erinnerungen werden direkt über den Kernen und ihrer 10nm + Matrix mit abgelegt 350 Mikron TSVs zur Zusammenschaltung. Zusammenfassend haben wir also insgesamt 5 Schichten auf einem Chip, der 12 mm2 und 1 mm hoch ist.

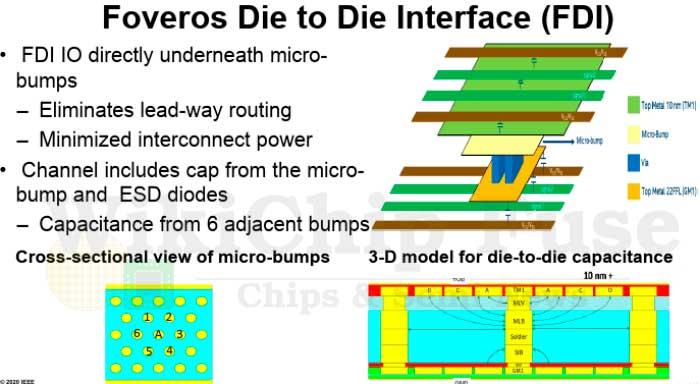

Die Kommunikationsschnittstellen werden mithilfe der von Intel als FDI oder Foveros Die Interface bezeichneten Schnittstelle hergestellt, wobei die maximale Geschwindigkeit zwischen den Matrizen liegt 500 MB/s und pro Spur. Wenn man bedenkt, dass es mehr als 200 Spuren mit demselben Takt hat, haben wir eine wirklich erstaunliche Bandbreite für einen Chip dieser Größe.

Um diesen Abschnitt abzuschließen, sollte berücksichtigt werden, dass diese Bereitstellung von Diäten mit einem anderen Formfaktor endet, der eine Stromversorgung durch die TSVs einschließt, die aufgerufen wurde PMIC und hat nichts mit den Spannungsreglern der mobilen U- und Y-Serie zu tun.

LakeField, die Zukunft des 3D-Stapelns

Wie wir schon gesehen haben Co-EMIB und ODI Die Zukunft des Unternehmens liegt in der Verbesserung der Aktivitäten von LakeField. Der erste Schritt wird darin bestehen, die Effizienz und die Kosten zu verbessern und schrittweise verschiedene Verbesserungen zu implementieren, die neue CAD-Erstellungssysteme, Netzteile, ESD, Signalintegrität und eine lange usw. erfordern.

Was Intel in kurzer Zeit suchen wird, ist die Kombination von Kernen mit geringem Stromverbrauch mit Kernen mit sehr hoher Leistung, einschließlich Xe GPUs mit HBM und das alles in demselben vertikalen 3D-Paket, das das Beste aller Welten bietet.