Es ist kein Geheimnis, dass AMD wird in Zukunft viel aus seiner vertikalen Cache-Technologie ziehen. Wir haben es bereits bei den EPYC Milan-X-Prozessoren für Server und im Ryzen 7 5800X3D für PCs gesehen. Die Pläne könnten jedoch weiter gehen und wir könnten über eine sprechen eventueller L4-Cache und KI in zukünftigen AMD Ryzen.

Der Cache-Speicher eines Prozessors hat eine klare Funktion, um die Ausführung von Befehlen zu beschleunigen. Dies darf jedoch beim Abrufen der Daten nicht langsamer sein als RAM. Damit ist der Punkt erreicht, an dem das Hinzufügen zusätzlicher Cache-Ebenen kontraproduktiv ist und nicht zu einer besseren Performance führt. Der Grund dafür ist, dass die Ebenen nicht fortlaufend sind und für jede der Ebenen ein zusätzlicher Zugriff erfolgen muss, bis der Systemspeicher erreicht ist.

Die Einführung von DDR5-Speicher und seine höhere Zugriffslatenz öffnen jedoch ein Zeitfenster für eine weitere Ebene in der Hierarchie. Was im Fall von Desktop-AMD Ryzen nicht in CCD-Chiplets angesiedelt wäre, sondern viel weiter. Insbesondere im integrierten Speichercontroller. Was ist ein L4-Cache in AMD-Prozessoren. Sowohl EPYC, Threadripper als auch Ryzen.

Woher wissen wir, dass zukünftige AMD-CPUs einen L4-Cache haben werden?

Die Antwort auf die Frage ist einfach, weder mehr noch weniger als ein Patent. Und es ist, dass AMD beabsichtigt, auf eine der Kapazitäten zu reagieren Intel hat im Moment. Wir beziehen uns auf die XMX-Einheiten innerhalb der auf Intel Core 12 und Sapphire Rapids basierenden Xeons. Das heißt, die Einheit des systolischen Array-Typs oder die Tensoreinheit zur Berechnung von Arrays. Mit anderen Worten: Algorithmen der künstlichen Intelligenz zu beschleunigen, damit sie flüssiger auf dem Prozessor laufen.

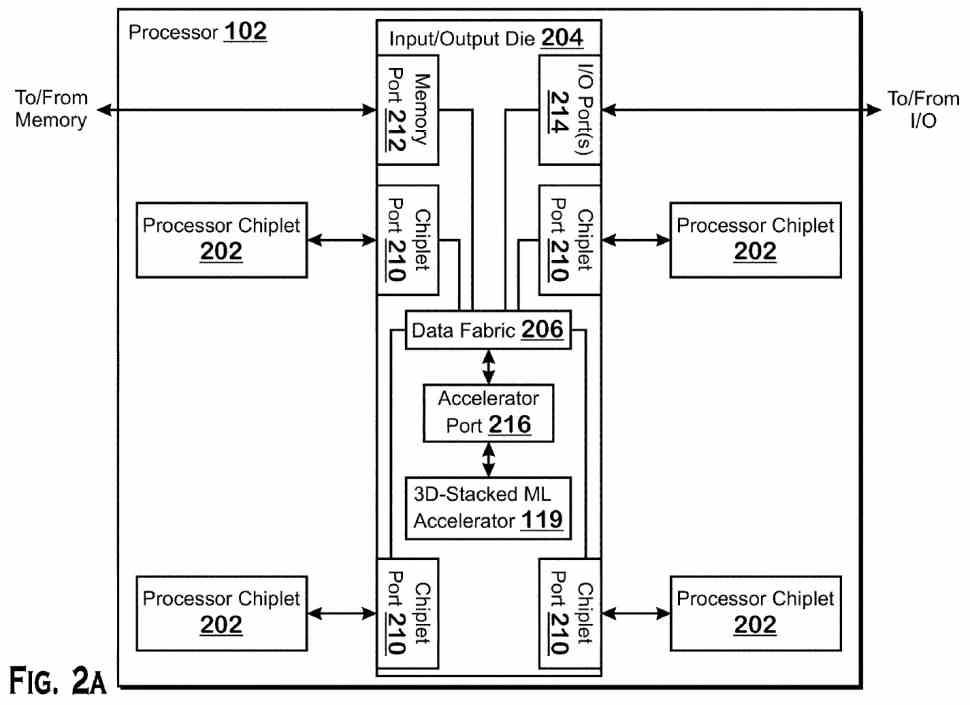

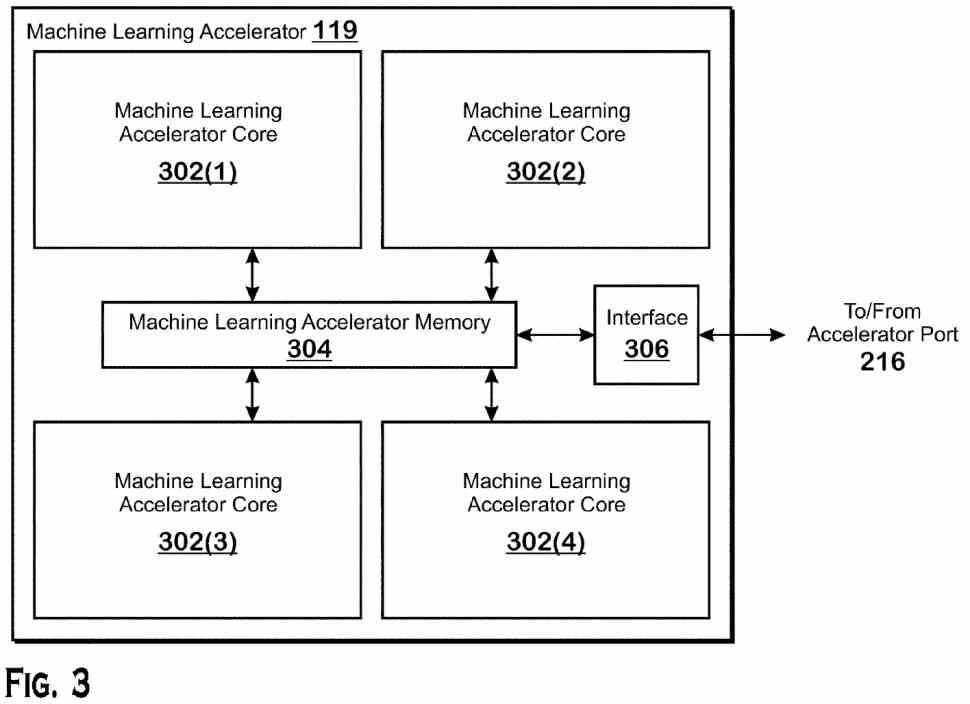

Zu diesem Zweck hat AMD eine neue IOD-Einheit geschaffen, die sich dadurch auszeichnet, dass einige der Ports für die verschiedenen Prozessoren geopfert werden, um dafür eine Einheit zur Beschleunigung von Machine-Learning-Algorithmen zu integrieren. Wir stehen also vor AMDs Reaktion auf die Aufnahme der XMX-Einheit in die neuesten Prozessoren seines Hauptkonkurrenten. Das Schöne daran ist, dass Intel sich dafür entschieden hat, dass einige seiner Xeon Sapphire Rapids HBM-Speicher verwenden. Bei AMD ist die Lösung einfacher. Die Verwendung derselben V-Cache auf dem Prozessor für KI, um die Algorithmen zu beschleunigen . Obwohl in diesem Fall in Form von L4-Cache . Ein bisher unerreichtes Niveau bei Prozessoren mit Zen-Architektur.

Im Augenblick das ist noch ein Patent, aber das wird wahrscheinlich dazu führen ein neuer CPU Variante . Auf jeden Fall ist es ein Markt, an dem AMD das geringste Interesse von allen gezeigt hat. Obwohl Gerüchte behaupten, dass diese Einheit tatsächlich eine sein könnte Embedded FPGA oder eFPGA von Xilinx . Darüber werden wir Zweifel lassen, wenn die Zeit gekommen ist.