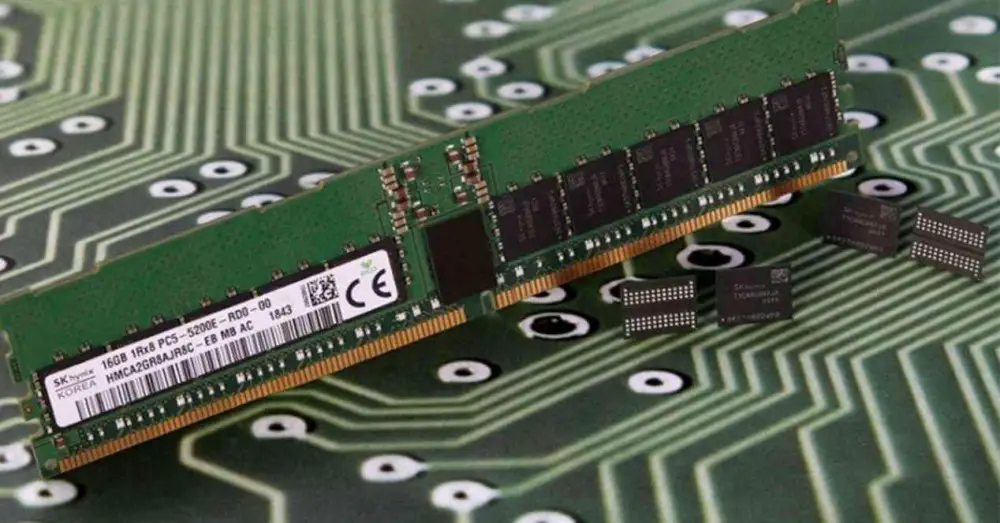

The next generation of RAM for PCs is the fifth generation DDR or DDR5. Which will mean an advance over the current DDR4 in terms of aspects such as bandwidth and energy consumption when transmitting data. However, DDR5 is an important change compared to previous DDR memory, which is why we explain how MT / s are measured in DDR5.

With the announcements of the first DDR5 memory DIMMs on the one hand and with the confirmation from AMD and Intel that their next generation PC CPUs, Alder Lake and Zen 4, will have DDR5 support. It turns out that DDR5 is going to become the next standard for PC RAM.

DDR5 memory overview

Before talking about the width of DDR5 bandwidth performance, we have to explain how it differs from its predecessor, DDR4. The first change being the most obvious of all, which consists of being able to achieve the same bandwidth using much lower consumption. Since the voltage necessary to reach the same clock speed on the memory interface is lower when going from 1.2 V to 1 V. All this combined with a voltage regulator integrated in the DIMM controller, which has moved from the system board to the DIMMs. Making the DDR5 voltage and speed setting no longer dependent on the motherboard.

Another important change is the use of the so-called On-Die ECC, which should not be confused with the fact that DDR5 is an ECC-type memory. The difference between the On-Die ECC and the standard ECC is that it only detects faults if they occur in the same memory cell or column. This means that the DDR5 does not have the classic parity pin of ECC memories where each byte of data that is transmitted is not 8 bits but 9 bits, in which the ninth bit is parity.

We cannot forget Burst Lenght, which has been increased and now allows feeding a cache line from RAM, which is usually 64 bytes, with only one access to memory. Decreasing latency and increasing bandwidth. It achieves this thanks to its ability to send 2 memory requests of 32 bytes each simultaneously thanks to the fact that the DDR5 supports 2 channels of simultaneous access per DIMM.

Speed and transfer in MT / s of DDR5 memory

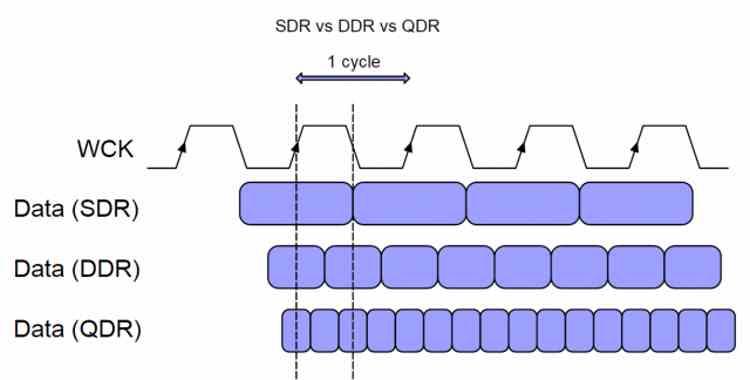

You will have seen that all RAM memory has in its specifications a data that puts a certain number followed by MT / s. Which indicates that it is a rate with respect to time, the M comes from Mega and refers to 1 million or 10 ^ 6 and the T refers to data transfers. How is transfer measured then? Well, very simple, memory has a clock speed called memclk, which is multiplied by one, by two or by four if we are talking about SDR, DDR or QDR memory.

Given that DDR5 is DDR memory of the DDR type, then the number of transfers per second is that of the memclk multiplied by 2. And here we have to give ourselves a general slap on the wrist, since when we talk about DDR5-4800 memory what we usually say is DDR5 at 4800 MHz, but this is false, since the memclk works in this case at 2.4 GHz really, but performs twice as many transmissions per clock cycle.

But there is one element that differentiates DDR5 memory from other DDR memory to date and that is the fact that it supports two memory channels per DIMM. Let’s not forget that the number of memory channels refer to the number of simultaneous requests that can be made to the memory module at the same time. Every memory request results in one transfer and since DDR5 can perform two transfers at the same time things get more confusing.

MT / s do not measure the amount of data that is sent per shipment. So despite the fact that DDR5 has gone from sending 64 bits of data per transfer to 32 bits per DIMM, the number of transfers has increased. So if we compare a DDR4-3200 module with a hypothetical DDR5-3200 module, the first will have a speed of 6400 MT / s, while the second of 12800 MT / s.

Twice as many memory banks as DDR4

Another change that has been made to DDR5 memory and that has to do with the support of 2 memory channels for access is the increase in the number of memory banks into which each DDR5 memory chip is subdivided. Since we have gone from 4 groups of 4 memory banks each to 8 groups also of 4 memory banks each. So internally, a DDR5 DIMM is like having 2 DDR4 DIMMs in terms of memory access.

This is not only beneficial when it comes to accessing the memory by the two access channels, and allowing the highest amount of MT / s. Since the advantage of dividing the RAM into a greater number of banks prevents contention from being created by the memory channels and therefore latency. Increasing the amount of effective and therefore real transfers per cycle that are made. Which translates into a lower latency when accessing the data by the CPU and with it a higher performance when executing the instructions.

Let’s not forget that the MT / s figure given by the manufacturers is a theoretical maximum of performance with the memory transmitting continuously without associated problems of any kind. So the actual MT / s amount of a memory is not as advertised, but it will be much more efficient in the case of DDR5 by its nature.