En god del af styrken i vores pc'er er baseret på arbejdsdelingen, hvor flere elementer deler udførelsen af en del af koden for at arbejde med den. Men nogle gange er der konflikter i adgangen til data og instruktioner, der bliver et ydeevneproblem. En måde at rette det på er transaktionshukommelse.

Et af de største problemer med multicore CPU Systemer, som vores pc'er bruger, er, at de er baseret på Von Neumann-modellen, hvilket er, at der kun er en delt hukommelse. Efterhånden som antallet af eksekveringsenheder, kerner, tråde og andre elementer, der arbejder parallelt i en CPU, øges. Flere og flere konflikter skabes mellem dem. Ikke kun ved at få adgang til dataene, men også i oplysningerne i de forskellige hukommelsesadresser og derfor værdien af de variabler, der bruges af programmerne. Der er mange metoder til at undgå disse konflikter, en af dem er transaktionshukommelse, som vi skal beskrive i denne artikel.

En introduktion til problemet

Når du skriver et program, er det kodet i en række instruktioner, der tilsyneladende udføres sekventielt. Men allerede med paralleliteten af instruktioner med en enkelt kerne midt i udførelsen kan forskellige eksekveringsenheder komme ind. Til dette skal vi tage højde for, at udførelsen ude af rækkefølge tilføjer den kompleksitet, at adgang til hukommelse og data under kørsel sker på en uordnet måde.

Når der er et stort antal anmodninger, ender det med at skabe en strid om at få adgang til den samme hukommelse. Dette får anmodninger til at blive forsinket længere og længere, hvilket øger hukommelsens latenstid med CPU'en på visse instruktioner og påvirker båndbredden. Til dette er der mekanismer, der undgår disse konflikter i hukommelsesadgang så meget som muligt på en sådan måde, at processerne får adgang til hukommelse fra ordnet hukommelse. Dette undgår konflikter, når du ændrer data i dets hierarki, samt reducerer konfliktproblemer og dermed adgangsforsinkelse.

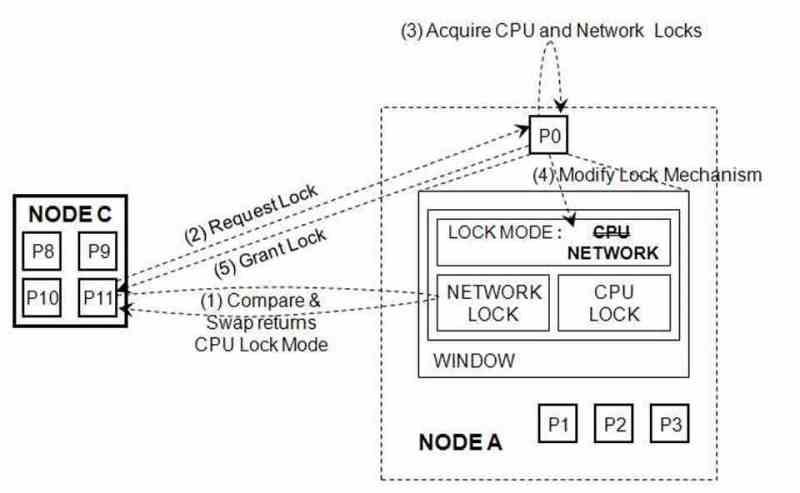

Den enkleste måde at opnå dette på er gennem låse, som er sektioner i koden, hvor vi markerer, at de ikke skal udføres samtidigt af forskellige tråde i CPU'en. Det vil sige, at kun en kerne af det kan være ansvarlig for denne del af koden. Så vi har lavet en lås til resten af kernerne, og resten vil kun være i stand til at komme ind i udførelsen, når den instruktion, der slutter låsen, er nået. Hvilket vil ske, når den del af koden, der er isoleret til alle kernerne undtagen en, er afsluttet.

Hvad er transaktionshukommelse?

En metode til at undgå de problemer, der er beskrevet i det foregående afsnit, er at bruge transaktionshukommelse. Hvilket ikke er en type hukommelse eller opbevaring, så vi taler ikke om et rent stykke hardware. Dens oprindelse er i databasernes transaktioner, det er en type instruktioner, der udføres i Load-Store-enhederne.

Transaktionssystemet i en processor fungerer som følger:

- Der oprettes en kopi af den del af hukommelsen, som flere kerner vil have adgang til, en for hver forekomst.

- Hver forekomst ændrer sin private kopi uafhængigt af resten af de private kopier.

- Hvis en data er blevet ændret i en privat kopi og ikke i resten, kopieres ændringen også i resten af de private kopier.

- Hvis to forekomster foretager en ændring af de samme data på samme tid, og det skaber en inkonsekvens i dataene, slettes begge private kopier. og de private kopier af resten kopieres

Det fjerde punkt er vigtigt, da det er i den del, hvor det bliver klart, at det er nødvendigt, at den del af koden serieliseres. Dette betyder, at de øvrige forekomster holder op med at ændre deres private kopier, og ændringerne foretages kun af en af forekomsterne. Når det slutter, kopieres ændringerne til resten af de private kopier. Når den del af koden, der er markeret som transaktion, allerede er blevet udført, og alle de private kopier indeholder de samme oplysninger, kopieres resultatet til de tilsvarende cachelinjer og hukommelsesadresser.

Transaktionelle hukommelsessystemer, Intel TSX

Forkortelsen TSX, Transaktionelle synkroniseringsudvidelser, refererer til en række yderligere instruktioner til x86 ISA, som er beregnet til at tilføje understøttelse af transaktionshukommelse Intel CPU'er. Derfor er det en række instruktioner og mekanismer, der er knyttet til dem, der gør det muligt at afgrænse bestemte sektioner af koden som transaktionsmæssige og for Intel CPU at udføre den proces, som vi har diskuteret i den foregående proces. Men i dette tilfælde er Intel-implementeringen lidt mere kompleks. Da, som vi har set før, hvis der er en konflikt mellem to data, afbrydes hele processen af en af de kørende forekomster.

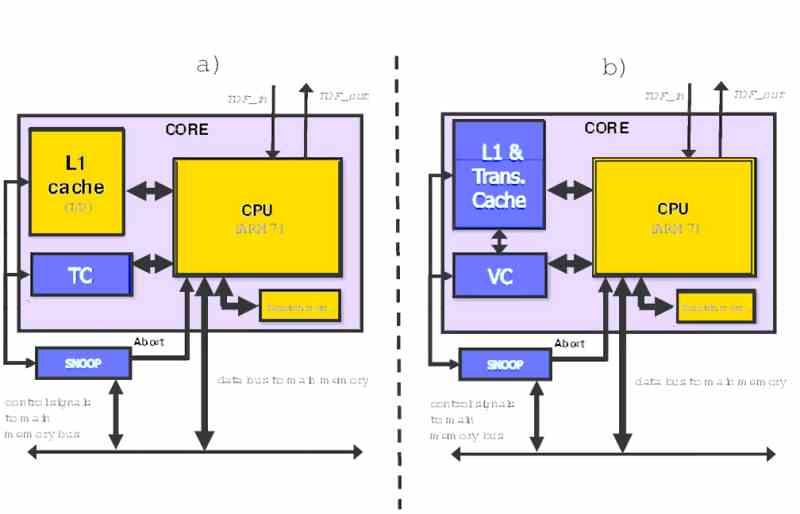

Dens implementering i hardware opnås ved at tilføje en ny type cache kaldet transaktionscache, hvor de forskellige operationer udføres på de forskellige data. Husk, at hvad transaktionshukommelse søger, er at reducere konflikter, når du får adgang til hukommelse. Selvom cacherne understøtter et større antal anmodninger end RAM generelt er disse også begrænsede og især på de niveauer, der er længst væk fra kernerne. Alt dette kombineres med brugen af interne minder og private registre, der tjener som støtte til de private kopier, der udføres af de forskellige kerner.

Intel TSX-instruktionerne er ikke et komplekst sæt, vi har på den ene side XBEGIN-instruktionen, der markerer os, når en transaktionsdel af hukommelsen begynder, XEND-instruktionen, der markerer slutningen, og XABORT, der tjener til at markere en udgang fra processen når der opstår en ekstraordinær situation.

Slutningen af Intel TSX instruktioner?

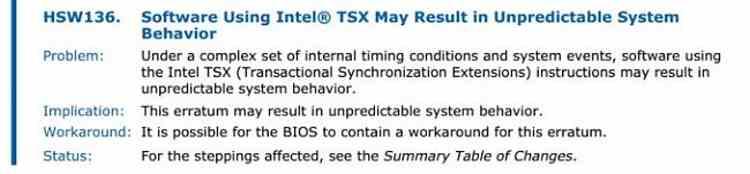

Dagens CPU-styreenheder er faktisk fuldblæst mikrokontrollere, det betyder, at den måde, det afkoder instruktioner på, og listen over instruktioner kan opdateres. Intel foretog den første implementering på Haswell-arkitekturen, og den har hidtil været inden for Intel-CPU'er. Da den for nylig er blevet deaktiveret via firmware på Intels egen sjette, syvende og ottende generationskerne.

Fra tid til anden udfører Intel fjernopdateringer af sine CPU'er, som udføres via Intel Management Engine, som vi har på vores pc, uden at vi ved det. De er normalt ikke almindelige, men kan omfatte optimeringer til udførelsen af visse instruktioner eller endda eliminering af støtte til andre. Eliminering af Intel TSX i Intel Core skyldes, at det med de seneste ændringer af den interne mikrokode på kontrolenheden indebærer en konflikt i softwaredriften, hvilket betyder, at CPU'en ikke fungerer som den skal.

Men den virkelige årsag er, at Intel TSX tillader, at ondsindet kode udføres under radaren fra klassiske sikkerhedssystemer, især det, der påvirker operativsystemet. Da de private kopier ikke svarer til brugerens miljø eller operativsystemet. Så det er stadig et problem svarende til spekulativ udførelse.