Forkortelsen SerDes for mange af jer vil lyde som at komme fra en anden verden, udenjordisk sprog, men de findes virkelig i alle typer hardware i dag og er et af de mest anvendte stykker til intern kommunikation mellem komponenterne i en processor såvel som ekstern kommunikation med andre komponenter. Men hvad er det, hvordan fungerer det, og hvor bruges dette stykke hardware?

På pc'en kommunikerer forskellige grænseflader med hinanden med CPU, APU eller GPU. Men hvad er det stykke, der forener de forskellige signaler, der kommer ind og forlader en processor? Vi forklarer, hvad dette almindelige stykke findes i al hardware, og hvordan det fungerer. Hvilket ofte kaldes SerDes.

Hvad er en SerDes?

SerDes har deres oprindelse i telekommunikationsverdenen. Årsagen til dets eksistens er ret enkel, at sende data via et enkelt kabel i stedet for flere på samme tid reducerer kompleksiteten af det interne intercom i et telekommunikationsnetværk. Hvis vi nu tænker over det, kommunikeres de forskellige logik- og hukommelsesdele af både en processor og et system gennem en række kabler.

Ved første øjekast kan det med hensyn til ydeevne virke som at bruge en parallel interface altid er meget bedre, men der er en række faktorer, der gør serielle grænseflader bedre. Som er? Først og fremmest optager parallelle grænseflader meget mere plads og er mere modtagelige for elektromagnetisk, bortset fra at forbruge mere ved samme klokkehastighed. Ulempen ved serielle grænseflader er, at de har en højere latenstid ved afsendelse af data.

Men i et hardware design er der dele med en seriel grænseflade og andre med en parallel grænseflade. Hvordan forbinder man dem til hinanden, deres kommunikationsgrænseflader er forskellige? Nå, med SerDes, hvis hovedopgave er at kommunikere forskellige elementer, især perifere enheder med CPU'en.

Alle veje fører til Rom

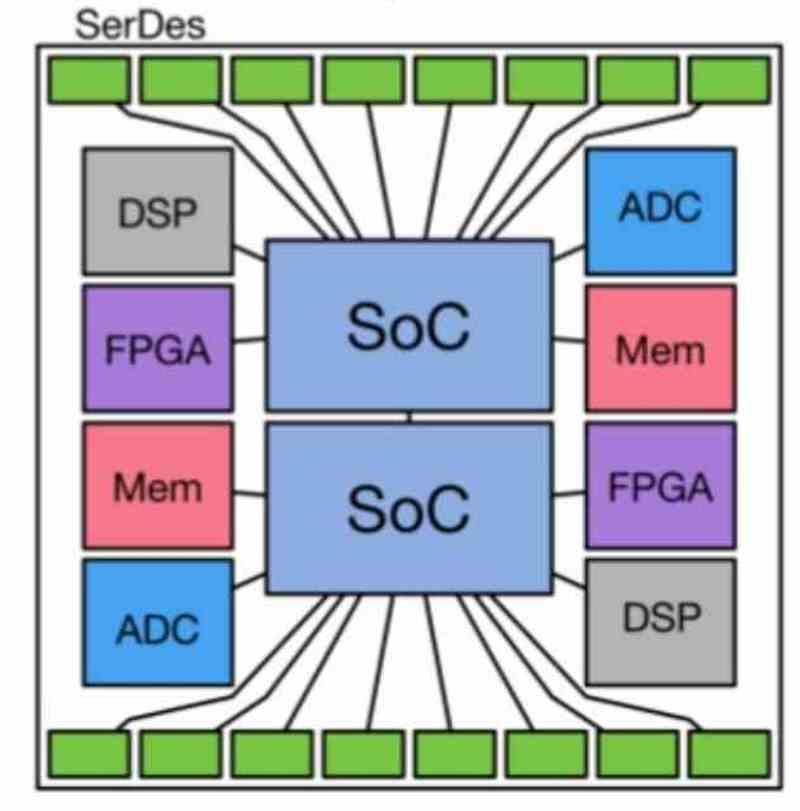

Se på din pc og de forskellige grænseflader til interne komponenter og eksterne enheder. Vi har grænseflader som SATA, PCI Express, USB og en lang osv. Hver af dem har grænseflader til forskellige typer perifert udstyr. Nå, internt forbinder hver af disse grænseflader ikke direkte til den centrale processorhub, men snarere til en række SerDES.

Ikke overraskende er der forskellige input- og outputgrænseflader til perifert udstyr af alle slags, der er designet til at interagere med standardspecifikationerne for de forskellige SerDes. Hvad er disse grænseflader? Nå, vi har tilfældet med PCI Express-grænseflader i deres forskellige teknologier, til lagring som SATA og SAS, til videooverførsel som DisplayPort og HDMI, til netværk som de forskellige gigabit ethernet-grænseflader osv. Men sagen er ikke kun begrænset til I / O-grænseflader til perifert udstyr og komponenter, men sagen går videre og RAM hukommelse kommunikerer også gennem en SERDES med det centrale hub, som hver processor har, kendt som Northbridge. og det har ansvaret for at kommunikere de forskellige elementer med hinanden og hver enkelt af dem med RAM-hukommelsen.

Derfor skal de forskellige grænseflader ikke kun, når de designer, men også udvikler sig, tage højde for udviklingen af SerDes i det øjeblik, da disse grænseflader vil være forbundet til disse i den interne logik i hvert integreret kredsløb. Det skal tages i betragtning, at internt i en processor, hvis der er for mange samtrafik, så vil kompleksiteten af interkommunikationen være for stor. Så det er bedst at reducere antallet af sammenkoblinger ved at serialisere de indgående data i bytte for at øge klokkehastigheden.

Hvordan fungerer en SerDes?

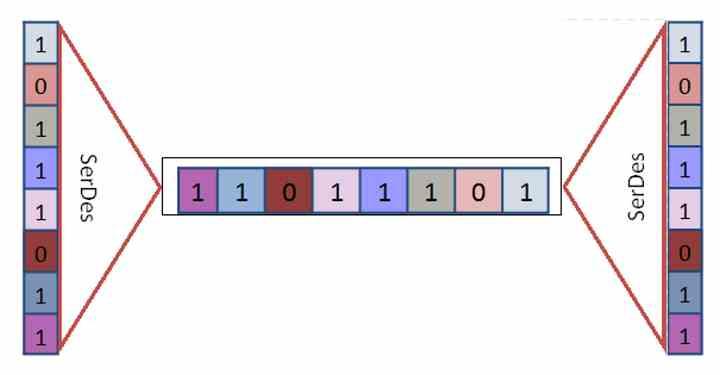

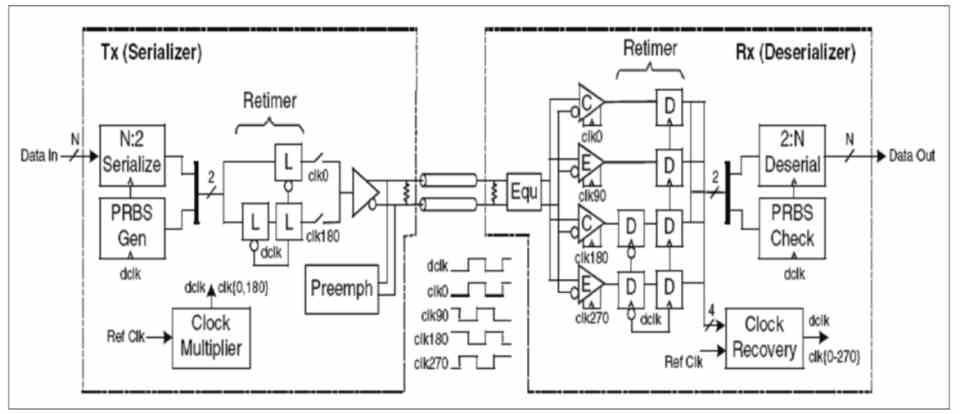

Hvis vi tager højde for denne rene og hårde definition, er SerDes stadig et stykke hardware sammensat af en multiplexer og en demultiplexer, som er to typer grundlæggende kombinationssystemer. Hvad en multiplexer eller MUX gør, er at konvertere et enkelt signal til flere forskellige signaler, og en demultiplexer eller DEMUX gør den modsatte opgave.

Forskellen er, at SerDES tager højde for klokkehastigheden, da afhængigt af hvornår dataene transmitteres, er fortolkningen af processoren den ene eller den anden. Med andre ord, når der foretages en dataanmodning fra en hvilken som helst komponent i et hardwaresystem, er der tidspunkter og derfor et vindue med mulighed for at overføre dataene. Hvad oversætter dette til? Nå, dataene transmitteres efter en tid, og det indebærer derfor et ursignal.

Antag, at vi vil serieisere et parallelt signal, der transmitteres gennem en række Full Duplex-linjer, der transmitterer 1 bit information i hver retning. Båndbredden er 1.25 Gbps, så det betyder, at hver linje fungerer ved 625 MHz. Vi har fire linjer i alt, så hvis vi serialiserer signalet, taler vi om et 5 Gbps-signal, hvilket i tilfælde af en fuld duplekslinje krævede, at det serielle interface fungerede ved 2.5 GHz. Den omvendte sti er derfor let at forstå, vi kan få 5 Gbps-signalet til at blive transmitteret gennem to linjer ved hjælp af en hastighed på 1.25 GHz for hver linje, gennem fire linjer ved hjælp af en clockhastighed på 625 MHz hver osv.

Udviklingen af SerDes

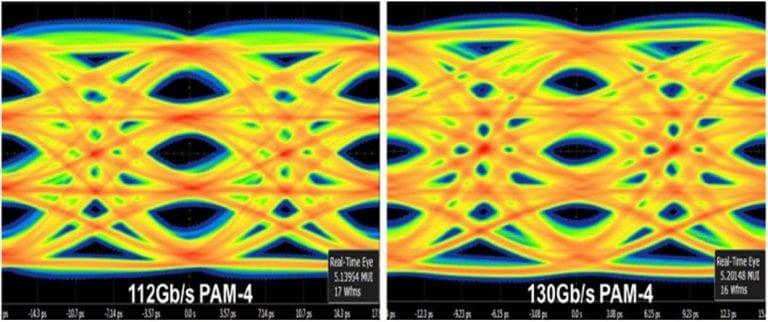

Før vi har kommenteret, hvordan SerDES fuldstændig påvirker designet af fremtidige input- og outputgrænseflader, hvilket indebærer, at udviklingen af fremtidige grænseflader eller udviklinger af eksisterende afhænger helt af de SerDes, som de er tilsluttet, da de skal være i stand til at kommunikere med dem. For eksempel bruger SerDES med 112 Gbps, den hurtigste hidtil på markedet, PAM4-signalering, derfor lyder denne type signalering for grænseflader som den fremtidige PCI Express 6.0.

At fremme kommunikationshastigheden på SerDes er imidlertid ikke en let opgave, for hver nye generation, hvor kommunikationsbåndbredden øges, dukker nye udfordringer op, især med de elementer, der forringer kvaliteten af det anvendte signal. transmittere. Vi kan heller ikke glemme, at spændingen ikke skaleres på samme måde som urets hastighed, hvilket får strømforbruget til grænsefladerne til at skyde i luften. Derfor er vedtagelsen af PAM4-grænseflader for at undgå at øge urets hastighed til grænser, der ikke ville være acceptabel.

I øjeblikket er kun GDDR6X-hukommelsen inde NVIDIA RTX 30 bruger PAM4-interface, hvilket betyder, at de interne SerDes i disse GPU'er bruger denne type interface til at kommunikere med GPU'en. Hvilket påvirker resten af I / O-grænsefladerne til disse GPU'er. Samtidig komplicerer dette vedtagelsen af et PAM4-system i andre systemer, da det betyder, at grænsefladerne skal tilpasse sig tidsreglerne for SerDes, der er inkluderet i processoren.