Et af nøglebegreberne til at forstå strømmens arkitektur og ydeevne Intel , AMD CPU'er er begrebet mikrooperationer, såvel som enheder som deres cache. I denne artikel vil vi fortælle dig på en tilgængelig måde, hvad de er, og hvorfor nutidens processorer baserer al deres drift på dem for at opnå den maksimalt mulige ydeevne.

A CPU i dag kan udføre en lang række forskellige instruktioner, og den gør det ved frekvenser, der er op til 5,000 gange højere end de tidlige personlige computeres. Vi har en tendens til at tro og helt forkert, at den større mængde MHz eller GHz skyldes de nye fremstillinger. Virkeligheden er meget anderledes, og det er her mikrooperationer kommer ind, som er nøglen til at opnå den enorme computerkraft i nutidens mikroprocessorer.

Hvad er mikrooperationer?

En af de lignelser med virkeligheden, der normalt bruges til at forklare, hvad et program er, er lignelsen med en madlavningsopskrift. I hvilket vi kan se tildelt i et verbum en række handlinger, som vi skal udføre. Jeg kan fx lægge en opskrift på, at du steger et stykke kød på panden, men for dig vil det vise sig at skulle lede efter panden, gør det samme med olien, kom sidstnævnte i panden, vent for at det bliver varmt og læg kødstykket deri. Som du kan se, har vi konverteret noget, der i princippet er defineret af et enkelt verbum, til en række handlinger.

Nå, instruktionerne fra en CPU kan opdeles i mindre, som vi kalder mikrooperationer. Og hvorfor ikke mikroinstruktioner? Nå, på grund af det faktum, at en instruktion, blot ved at segmentere den i flere cyklusser for dens udførelse, tager flere clock-cyklusser at løse. En mikrooperation tager på den anden side en enkelt urcyklus.

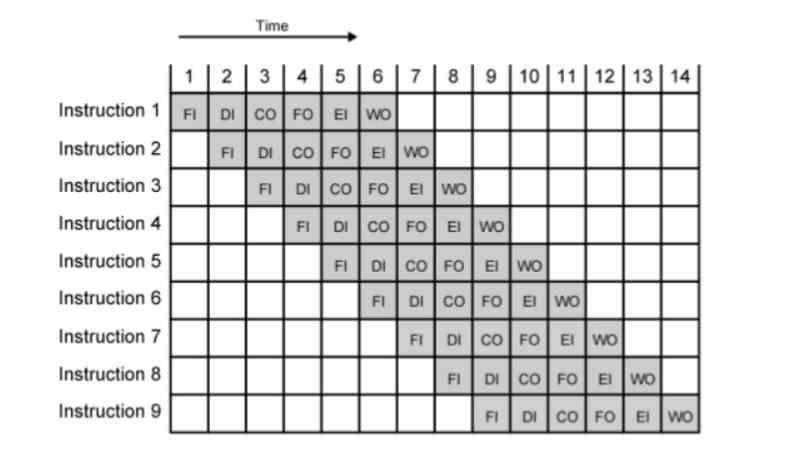

En måde at få mest muligt MHz eller GHz på er pipelining, hvor hver instruktion udføres i flere trin, der hver varer en clock-cyklus. Da frekvens er det omvendte af tid, er vi nødt til at forkorte tiden for at få mere frekvens. Problemet er, at det punkt er nået, hvor en instruktion ikke længere kan dekomponeres, antallet af trin i pipelinen bliver kort og dermed den clockhastighed, der kan opnås, er lav.

Faktisk blev disse født med udseendet af den ude af drift af Intel P6-arkitekturen og dens afledte CPU'er såsom Pentium II og III. Grunden til dette er, at segmenteringen af P5 eller Pentium kun tillod dem at nå lidt over 200 MHz. Med mikrooperationerne, ved at forlænge antallet af trin i hver instruktion endnu mere, overgik de GHz-barrieren med Pentium 3 og var i stand til at have clockhastigheder 16 gange højere med Pentium 4. Siden da er de blevet brugt i alle CPU'er med udelukket udførelse, uanset mærke og register og instruktionssæt.

Dine CPU'er er hverken x86 eller RISC-V eller ARM

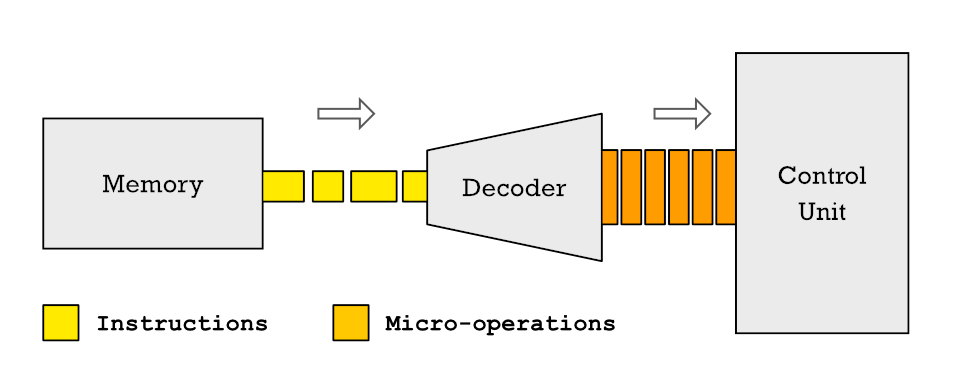

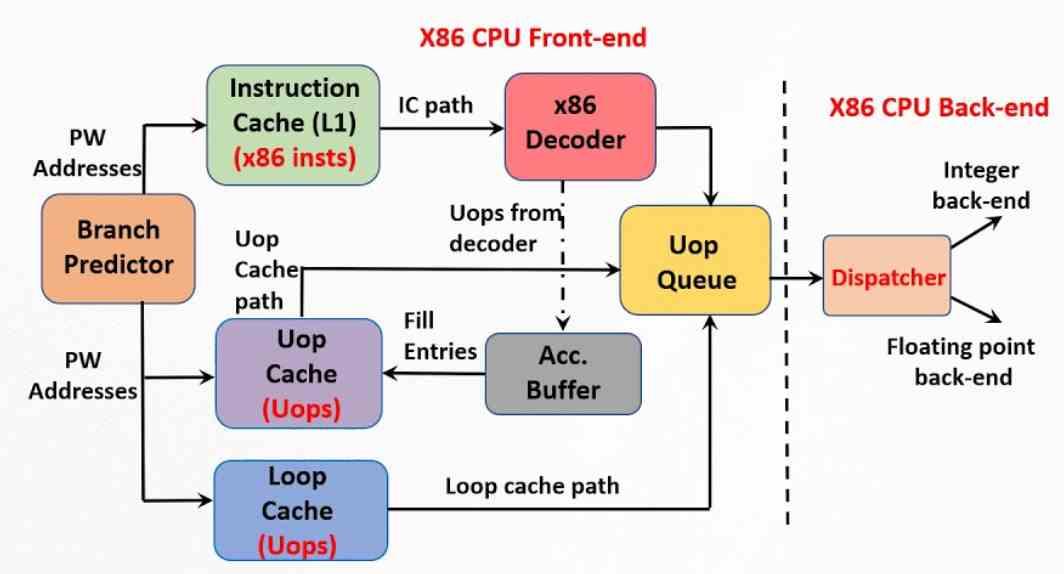

I nuværende CPU'er, når instruktioner ankommer til CPU-kontrolenheden for at blive afkodet og tildelt styreenheden, bliver de først opdelt i flere forskellige mikrooperationer. Det betyder, at hver instruktion, som processoren udfører, består af en række grundlæggende mikrooperationer, og sættet af dem i et ordnet flow kaldes mikrokode.

Nedbrydning af instruktioner til mikrooperationer og transformation af programmer gemt i RAM til mikrokode findes i dag i alle processorer. Så når din telefon er ISA ARM CPU eller din pc's x86 CPU udfører programmer, dens udførelsesenheder løser ikke instruktioner med disse sæt af registre og instruktioner.

Denne proces har ikke kun de fordele, som vi har forklaret i det foregående afsnit, men vi kan også finde instruktioner, der, selv inden for den samme arkitektur og under det samme sæt af registre og instruktioner, er opdelt forskelligt, og programmerne er fuldt ud kompatible. Ideen er ofte at reducere antallet af krævede clock-cyklusser, men det meste af tiden er det for at undgå den strid, der opstår, når der er flere anmodninger til den samme ressource i processoren.

Hvad er micro-op cachen?

Det andet vigtige element for at opnå den maksimalt mulige ydeevne er mikrooperationscachen, som er senere end mikrooperationerne og derfor tættere på tiden. Dens oprindelse kan findes i den sporingscache, som Intel implementerede i Pentium 4. Det er en udvidelse af første niveaus cache for instruktioner, der gemmer sammenhængen mellem de forskellige instruktioner og de mikrooperationer, hvor de tidligere er blevet adskilt af kontrolenheden .

Imidlertid har x86 ISA altid haft et problem med hensyn til RISC-typen, mens sidstnævnte har en fast instruktionslængde i koden, i tilfælde af x86 kan hver af dem måle mellem 1 og 15 bytes. Vi skal huske på, at hver instruktion hentes og afkodes i flere mikrooperationer. For at gøre dette er der også i dag brug for en meget kompleks styreenhed, der kan forbruge op til en tredjedel af sin energieffekt uden de nødvendige optimeringer.

Mikrooperationscachen er således en udvikling af sporingscachen, men den er ikke en del af instruktionscachen, den er en hardwareuafhængig enhed. I en mikrooperationscache er størrelsen på hver af dem fastsat i forhold til antallet af bytes, hvilket gør det muligt for f.eks. en CPU med ISA x86 at fungere så tæt som muligt på en RISC-type og reducere kompleksiteten af kontrolenheden og med den forbrug. Forskellen fra Pentium 4 plot-cachen er, at den nuværende micro-op-cache gemmer alle mikro-ops, der hører til en instruktion, på en enkelt linje.

Hvordan virker det?

Det, som mikrooperationscachen gør, er at undgå arbejdet med at afkode instruktionerne, så når dekoderen lige har udført opgaven, er det, den gør, at gemme resultatet af sit arbejde i cachen. På denne måde, når det er nødvendigt at afkode den følgende instruktion, er det, der gøres, at søge om de mikrooperationer, der danner den, er i nævnte cache. Motivationen for at gøre dette er ingen anden end det faktum, at det tager kortere tid at konsultere nævnte cache end ikke at dekomponere en kompleks instruktion.

Den fungerer dog som en cache, og dens indhold flyttes over tid, efterhånden som der kommer nye instruktioner. Når der er en ny instruktion i instruktionscachen på første niveau, søges der i mikrooperationscachen, hvis den allerede er afkodet. Hvis ikke, så fortsæt som normalt.

De mest almindelige instruktioner, når de først er nedbrudt, er normalt en del af mikrooperationscachen. Det, der dog får færre til at kassere, er, at de, hvis brug er sporadisk, vil være det oftere, for at give plads til nye instruktioner. Ideelt set bør størrelsen af mikrooperationscachen være stor nok til at gemme dem alle, men den skal være lille nok, så søgningen i den ikke ender med at påvirke CPU'ens ydeevne.