Det store flertal af jer er helt sikkert ikke klar over, at vi står på randen af en korsvej, hvad angår CPU , GPU er bekymret. Der er ikke meget margin, der er ikke meget tid, og det, der er tilbage, er ved at løbe tør. Der er behov for en ændring i en så grundlæggende komponent som konceptet med selve beregningen: i transistoren. Intel har sin vision af problemet og en løsning: dette vil være Intel RibbonFET.

For at forstå løsningen skal vi først være opmærksomme på problemet, forstå det og vide, hvad grænserne er, der vil markere os, så i dette tilfælde starter vi der, med problemerne med transistorer i dag. En transistor er den mindste elektriske enhed, der kan fremstilles til en elektronisk komponent, et elektrisk element som sådan, der er lavet af halvledere og optaget af utroligt avancerede scannere ved hjælp af en bølgelængde på spejle.

Det er dybest set en kontakt, der er forbundet mellem snesevis af lag af silicium (som en generel regel) af en meget lille størrelse, og som har en ekstremt klar funktion: at ændre strømmen af strøm, der passerer gennem den, give efter eller skære den. Hvert snit eller trin repræsenterer enten et nul eller et i binært, og med tiden er det opnået at forbedre det, hvilket giver mere hastighed i tilstandsændringen, mere eller mindre energi til nævnte ændring og mere eller mindre effektivitet, når det lades det nuværende pas.

Vi nærmer os kanten af transistorteknologi

Som vi allerede har tænkt, har hver transistor en række designs, der varierer alt efter producenten. Intel har sin vision, TSMC det samme og Samsung mere af det samme, så selvom alle mere eller mindre er kopieret i fremskridtene, er implementeringen og forbedringerne forskellige.

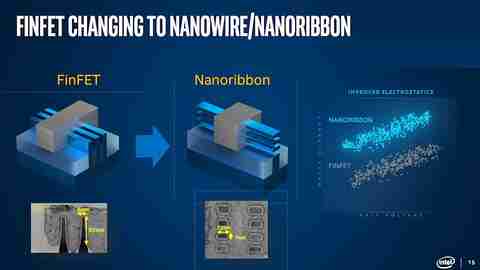

For ti år siden introducerede Intel FinFET-transistoren, som er blevet valgt af alle producenter, men det design er ved at være slut af flere grunde. Med denne type transistor havde vi et fleksibelt design af samme, normalt brede, hvor flere porte krydsede den, hvilket gav producenterne mulighed for bedre at kontrollere energistyring, svejsning og byggematerialer, samt fortsætte med at reducere dens størrelse i nanometer.

Det største problem, vi har, er simpelt: det kan ikke reduceres meget mere i størrelse, da vi har begrænset langsgående plads, og portene på hver transistor ikke kan slutte sig mere uden at miste elektroner. Hertil skal tilføjes, at afstanden mellem dem er så lille, at svejsning og sammenkobling kræver uhyre dyre nye materialer og legeringer, nogle stadig eksperimenterende, som garanterer passage af energi og ikke udløser prisen.

Hvad er løsningen? En ny type transistor, der ikke kun tillader flere lag at drive strøm, forbedre kontrol, svejsning og effektivitet, men også reducere afstanden mellem transistorer til Ångstrøm (molekylær og atomare måleenhed).

RibbonFET, Intels løsning på den nye grænse for litografi

Hvis du ikke kan blive ved med at reducere pladsen og kontrollere alle parametre uden at udløse omkostningerne, er det kun tilbage at undersøge en ny vej. Denne nye vej i form af en ny arkitektur for transistoren kaldes GAA eller også kendt som Gate-All-Around. Herfra er konceptet opdelt i tre aspekter eller endda 4 (det er ikke helt klart):

- TSMC GAAFET .

- Samsung MBCFET .

- Intel Bånd FET .

- Global Foundries er i et limbo med rygter, men intet konkret.

Hvad sker der her? Nå, som det skete med FinFET, vil GAA have flere varianter, alle baseret på det samme transistorkoncept. Vi har allerede talt om Samsung MBCFET, GAAFET er endnu ikke blevet afsløret som sådan, selvom det vil ankomme med virksomhedens 2 nm, så efter præsentationen af Intel i dets Architecture Day 2021 og efter at have afsløret nogle flere detaljer, vil vi kende væddemålet af den gigantiske blå: RibbonFET.

Konceptet er enkelt, men svært at implementere. De tager en transistor med fleksibel bredde, som vil blive reduceret med hvert litografisk spring, og som tillader flere lag, nu kaldet nanosheets, dry sheets eller finner af industrien, at blive forbundet lodret på transistoren i stedet for vandret. Hvad opnås? Nå, først og fremmest, reducer i høj grad transistorens bredde, tillad flere nanoark på en mindre overflade og frem for alt en enkelt port, der vil kontrollere al cellens energi.

Elektrostatikken er blevet enormt forbedret, som Intel viste i sin officielle præsentation, hvor vi kun skal se størrelserne på Pitch Gate og Gate Stack. Det går fra 6 nm x 50 nm til 12 nm x 7 nm og med mere kontrol nanosheets og bedre loddet.

Et variabelt nanoark design efter transistorens behov

Tilsyneladende, og som vi har set i forskellige dokumenter, siden Intel talte om denne nye type transistor, ser det ud til, at den blå gigant kan indsamle et variabelt antal nanoark pr. transistor.

Denne detalje er vigtig, da Intel går ned i litografien baseret på bedre EUV-scannere, vil den enten være i stand til at beholde det samme antal eller fjerne dem, der skal til for at optimere hver Gate. Dokumenterne viser fra 2 til 5, men i det sidste datablad ser det runde tal ud til at være 4. Flere finner / nanoark kræver flere trin for at skabe transistoren, så det hæver prisen på hver chip, så muligvis vil Intel starte med et tal betyder af dem, indtil du har forbedret gravering og produktionskontrol, materialer og svejsninger, der giver dig mulighed for at eliminere en række bestemte nanoplader og reducere omkostningerne uden at gå på kompromis med stabiliteten, hastigheden eller effektiviteten af transistorerne.

Dette vil logisk afhænge af højden af porten og med det antallet af ark, som vi kan installere i den, da nu i stedet for at være omgivet af tre steder, som det skete i FinFET, er hver ende fuldstændig omgivet af porten, hvilket betyder en side er optimal, men den anden gør det svært at reducere højden mellem arkene.

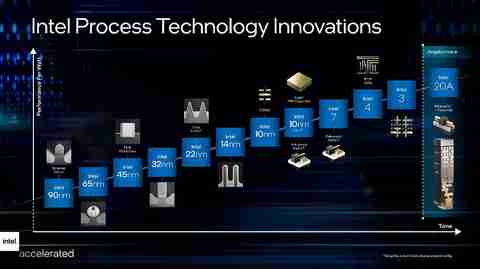

Hvornår vil Intel RibbonFET implementere i sine chips? Ifølge virksomheden selv i 2024, helt sikkert ved udgangen af samme år, hvis alt går godt, selvom vi kunne se det i midten af samme år, hvis det var glat. Under alle omstændigheder vil det være dens 20A litografiske proces, der inkluderer den og vil konkurrere med TSMCs GAAFET og Samsungs MBCFET . Intel er så sikker på, at det vil gøre en forskel, at det allerede har udtalt, at det vil lede halvlederindustrien og dens teknologi igen i 2025 – uden tvivl en hensigtserklæring.