Gennemførelsen af Infinity-cache i GPU'er med RDNA 2-arkitektur har været en af nyhederne i det nye AMD GPU arkitektur, men spørgsmålet, der kommer til at tænke på, er: er det noget eksklusivt for AMD GPU'er, eller skal vi se Ryzen-processorer, både i CPU'er og SoC'er?

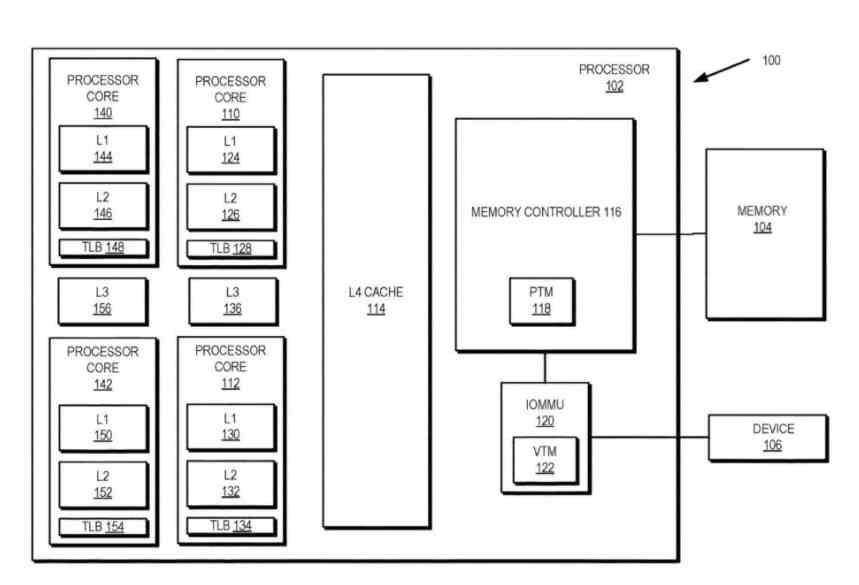

For et par måneder siden lækkede diagrammet for et AMD-patent, hvilket svarede til en processor fra AMD Ryzen-familien, eller det antager vi, men med det særlige at vise en cache på fjerde niveau i diagrammet, noget hidtil uset i AMD-processorer baseret på en sådan arkitektur.

Samtidig bringer udseendet af Infinity Cache i AMD GPU'er to spørgsmål i tankerne: vil vi se Infinity Cache implementeret i AMDs AMD Ryzen-processorer, vil den blive brugt som en L4-cache eller på en anden måde?

Hjælpekonflikten i Infinity Cache og L3 Cache i Zen-kernerne

Både L3-cachen i Zen-kernerne og Infinity-cachen i RDNA 2-arkitekturen udfører den samme funktion, da begge er Victim Caches og derfor har den samme funktionalitet. Dette betyder, at når det kommer til at indfange data og instruktioner til hver af deres tilsvarende processorer, er de ansvarlige for at indsamle cachelinier, der er kasseret af det tidligere cache-niveau.

Hvad er problemet? For at forstå det skal vi tage højde for, hvor Infinity Cache ville gå, hvis det blev implementeret i både en SoC og en AMD CPU, lige før hukommelsescontrolleren og derfor i Northbridge, som en formodet L4-cache.

Hvad er konflikten? Det giver ingen mening, at der er en offercache af en anden offercache, da Infinity Cache i dette tilfælde ville være forbundet med L3-cachen i Zen-kernerne, hvilket forårsager en funktionskonflikt mellem begge parter.

Infinity Cache-forbindelse er i konflikt med Zen-kerner

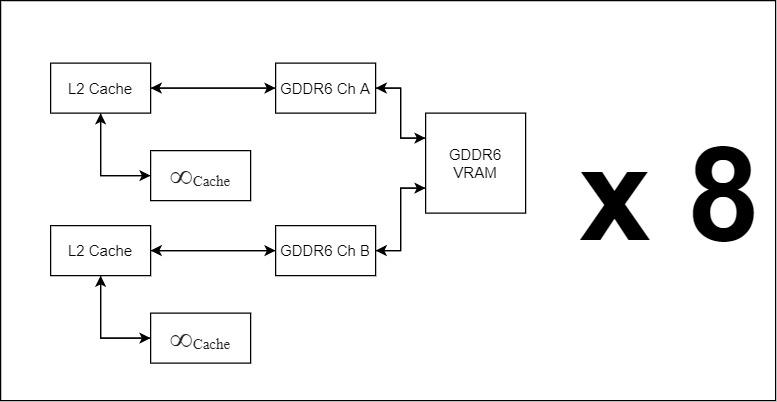

Hvis vi kigger på Infinity Cache på Navi 21 GPU, finder vi ud af, at der er 16 partitioner i alt, forbundet i den ene ende til 16 L2-cachepartitioner under en 64-byte / cykelbus for hver partition og i den anden ende til 16 kanaler GDDR6.

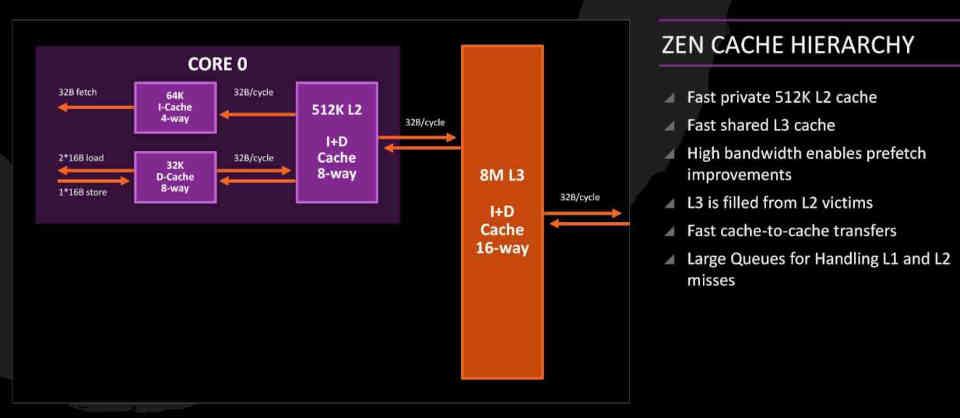

Ryzen-processorenes Zen-kerner er grupperet i en 4-kerne (Zen og Zen 2) eller 8-kerne (Zen 3) CCX, men CCX bruger et enkelt Infinity Fabric-interface, så den formodede Infinity Cache på en enkelt Zen-processor det ville bestå af et antal partitioner, der mindst svarer til antallet af CCX'er.

Så i en konfiguration med en CCD ville du kun have en partition, en med to partitioner 2 CCD'er, og det ekstreme tilfælde ville være noget som en AMD Epyc med 8 CCD'er, der ville have 8 partitioner. Generelt øges caches i størrelse med hvert ekstra niveau, og det er altid dobbelt så meget som det tidligere cache-niveau.

En enkelt Zen 3 CCD har en kapacitet på 32 MB L3 Cache, en enkelt partition af Infinity Cache er 8 MB, en meget lavere figur end hvad den skal bruge for at fungere som L4 Cache af en Zen-processor, så i forbindelse er det bevist, at Infinity Cache ikke kan fungere som L4 Cache for en processor med Zen CPU.

Og hvad med de integrerede GPU'er?

Da vi har set, hvordan Infinity Cache ikke kan bruges som en ekstra cache af Zen-kernerne, er det eneste svar, der er tilbage, som Infinity Cache af RDNA 2-kernerne integreret i SoC'erne, i øjeblikket har AMD ikke lanceret nogen SoC med en integreret RDNA-arkitektur GPU, på grund af lanceringstimingen tror vi ikke, at vi vil se den første generation af RDNA.

I tilfælde af iGPU'er giver det mening at integrere en Infinity-cache, der er placeret mellem hukommelsescontrolleren og grafikprocessoren, men det ville være til eksklusiv brug af grafikprocessoren i SoC.