Et par uger siden, ARM introducerede den niende generation af sæt registre og instruktioner, der blev brugt i processorer med ISA med samme navn. ARMv9 er navnet, hvorunder den nye version af denne ISA er blevet døbt, som vil blive brugt i fremtidige SoC'er til PostPC-enheder. Hvad er ARMv9, og hvad er nyt ved tidligere versioner, hvordan vil de fremtidige ARM-CPU'er se ud?

En ISA er intet andet end det sprog, som de forskellige processorer forstår, og markerer derfor, hvad sæt af nuller og nuller betyder i den kode, de udfører. Den binære for en x86 CPU har ikke den samme betydning som for eksempel en binær for en ARM-CPU.

Fremskridt inden for teknologi gør det imidlertid nødvendigt at tilføje nye instruktioner til ISA'erne, hvilket giver dem muligheden for at tilføje nye funktioner for at øge deres ydeevne, sikkerhed ved behandling af data eller at møde nye udfordringer, der præsenteres for dem.

I denne artikel skal vi tale om den niende generation af ISA ARM, som efter år rettet mod CPU'er og mikrokontrollere med lavt forbrug har besluttet at være mere ambitiøse og komme ind på det marked, der kræver den højeste ydeevne, datacentre og høj ydeevne computing eller HPC.

Skalerbare vektorudvidelser 2

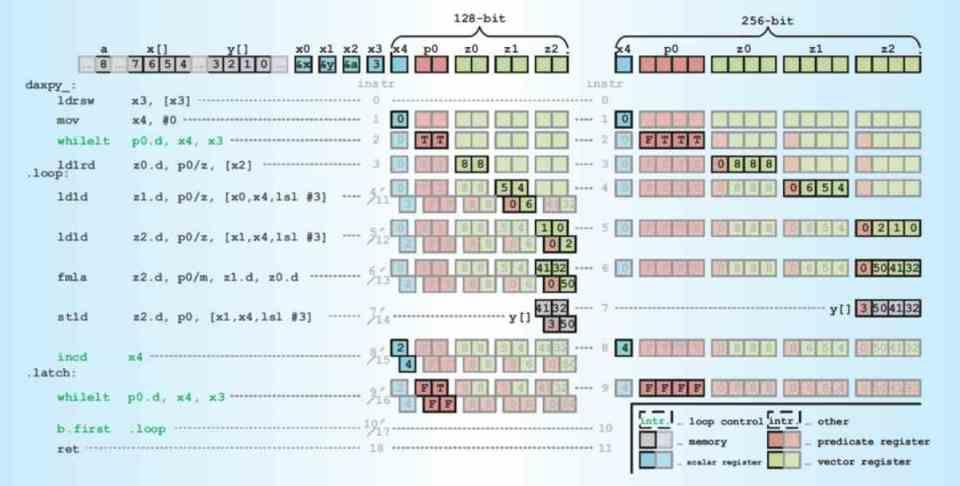

Den japanske Fujitsu oprettede for sin ARM-kerne en række proprietære udvidelser kaldet SVE, som står for Scalable Vector Extensions. Fra dets navn har du måske gættet, at vi taler om et sæt SIMD-instruktioner. Lad os ikke glemme, at i CPU'er med ISA ARM i årevis er Neon-instruktionerne blevet brugt. Hvilket vil blive erstattet af SVE2-instruktionerne i ARMv9.

SVE blev skabt af Fujitsu til sin Fugaku supercomputer, som bruger sine A64-FX kerner. Intentionen? Udnyt den dataparallelisme, der kræves af videnskabelig databehandling, der bruger højere præcisionstal. Dette oversættes til meget større SIMD-enheder og derfor flere bits.

Da ARMs interesse er at bringe deres kerner til det højtydende computermarked og servere, har de besluttet at vedtage SVE og fusionere det med Neon for at oprette SVE2. Den største fordel, som SVE tilføjer til Neon? Dette er størrelse-agnostiske instruktioner, så det er ikke nødvendigt at have en version af hver instruktion til forskellige størrelser, som det er tilfældet med AVX-instruktioner på x86.

Hukommelsesrige i ARMv9

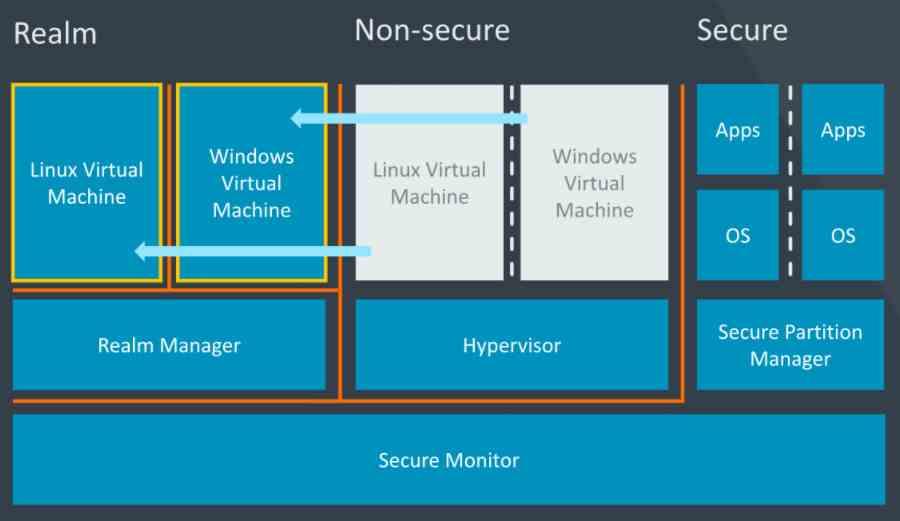

Et interessant koncept, som ISA ARMv9 tilføjer til ligningen, er begrebet riger, som består i at være i stand til at tage en del af hukommelsesadresseringen og gøre koden, der udføres i den, ikke påvirker resten af systemet, derfor er det helt isoleret. Hvilket er ideelt til implementering af virtuelle maskiner, hvor et operativsystem kører på samme tid som et andet på den samme CPU.

Normalt har CPU'er forskellige niveauer af privilegium, men med realms-konceptet, der er tilføjet i ARMv9, vil det være lettere at køre virtuelle maskiner på en CPU med ARM ISA, men fordelene ved dette er ikke kun begrænset til virtuelle maskiner, men kan også bruges i specifikke applikationer.

Så ARMv9 ser ud til at være en udvidelse til ISA, der er mere forberedt på datacentre og andre typer computere, hvor virtualisering og sikkerhed er meget vigtigere end andre funktioner. Ikke overraskende fører ARM en krig mod Intel , AMD på server-CPU-markedet, hvor x86-processorer dominerede markedet indtil nu.

Extensions til hukommelsesmærkning

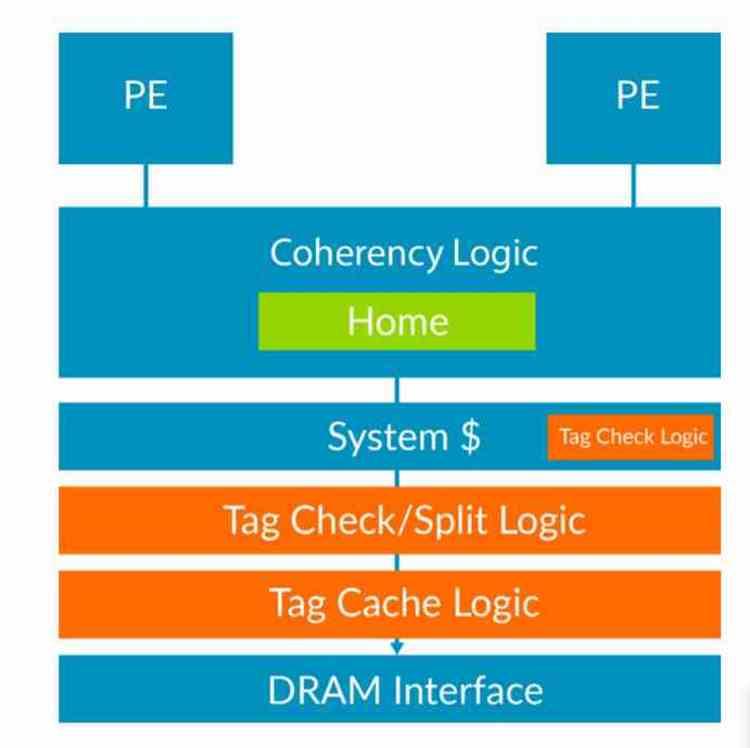

De er ikke nye for ARMv9, men snarere for version 8.5. Dens nytte? Det er en mekanisme, der har ansvaret for at holde styr på al ulovlig hukommelsesadgang foretaget af programmer. En ulovlig adgang er intet andet end en adgang til en hukommelsesadresse, som programmet ikke har adgang til. Hvad er nytten af dette? Da det tjener til at undgå det såkaldte bufferoverløb, er et almindeligt sikkerhedsproblem i alle processorer, der opstår, når mængden af data, der kopieres, overstiger hukommelsesreserven og skriver uventet kode i nærliggende hukommelsesadresser.

Hvis hukommelsesoverløbet er vellykket, erstattes den originale kode af ny kode i hukommelsen, som udføres af CPU'en, så snart den når hukommelsen. Så det er vigtigt at undgå dette, især hvis vi taler om datacentre, der har tendens til at betjene millioner af brugere på samme tid, og hvor et bufferoverløb kan bruges til at stjæle kompromitterede brugerdata.

MTE er ikke en del af selve ISA, men er en mekanisme implementeret i Northbridge af ARMv9-CPU'er, der sporer al hukommelsesadgang, og hvis funktionalitet er at undgå hukommelsesoverløb på en gennemsigtig måde.

ARMv9 kun til datacentre og servere?

Nyhederne i ISA ARMv9, som vi har beskrevet i de foregående afsnit, har en markeret specifik karakter og har intet at gøre med brugen i de klassiske enheder, hvor ISA ARM normalt ses. Af dem alle kalder det SVE kraftigt, da en af grundene til, at du normalt ikke ser store SIMD-enheder i CPU'er til PostPC-enheder, er det enorme energiforbrug, som deres brug antager.

I øjeblikket er de eneste to kerner, der er annonceret af ARM, to fra familien Neoverse. På den ene side NeoVerse V1 under kodenavnet “Zeus” og på den anden Neoverse N2 under kodenavnet “Perseus”. Dette er ikke kerner, som du vil se i en fremtidig smartphone, men i datacentre og servere til højtydende computing af virksomheder som Amazon AWS, Oracle, Tencent, Google osv.

ARM har endnu ikke annonceret nogen kerne til PostPC-enheder såsom smartphones og tablets. Selvom vi ikke kan glemme, at målet med ARM er at fortrænge x86 på forskellige markeder, ikke kun på servere, men også på pc'en. Købet af NVIDIA og dets store indflydelse på pc-videospilmarkedet kan bringe ankomsten af gaming-pc'er med ARM'er og NVIDIA GPU'er, selvom det er en fremtid, der har brug for en masse støtte fra udviklerne af videospil og ikke selve NVIDIA-ARM.