Hvis der er noget tydeligt i processor industri, er det det Intel , AMD dominerer markedet fuldstændigt i et duopol, der synes uovertruffen. Men i nyere tid ODM (dette betyder, at de ikke fremstiller chips, de designer dem kun) ARM får mere og mere betydning, især med design som f.eks DynamiIQ , et væddemål, der lover at forbedre kraften af processorer, mens vi opretholder forbruget, og i denne artikel vil vi fortælle dig, hvad det består af.

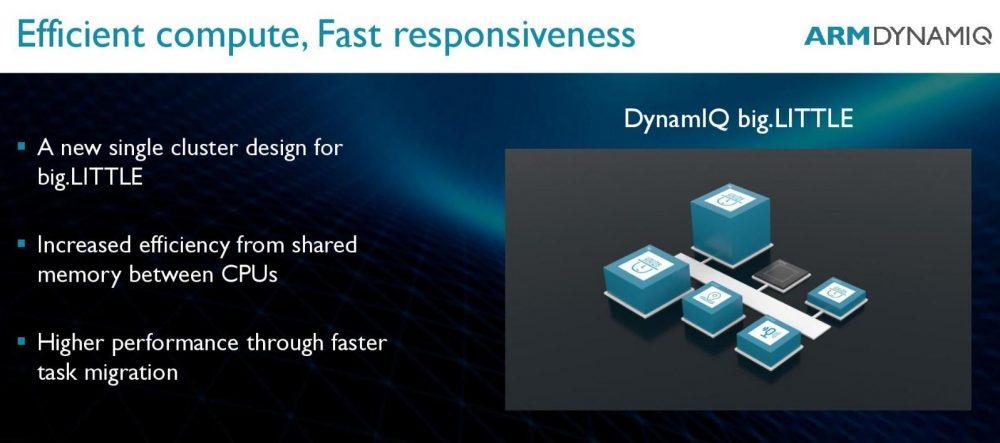

Faktisk, hvis der er et ARM-design, der er kendt, er det det big.LITTLE , bestående af en heterogen arkitektur, der består af større og mere kraftfulde kerner til at udføre krævende opgaver og andre mindre og laveffektive kerner for at spare energi, når udstyret ikke gør det. kræver stor kraft. Denne arkitektur er blevet implementeret i smartphone-chips i lang tid og ikke længe siden, at Intel (og det ser ud til, at AMD med Zen 5) har vedtaget et lignende paradigme (men på sin egen måde) i sine desktop-processorer, så alt peger som er vejen at gå.

ARM DynamIQ, hvordan man øger strømmen uden at øge forbruget?

ARM-arkitekturen har kørt i mange år som et alternativ til Intel og AMD, men især i mobiltelefoner og servere takket være det lave forbrug, men det var først Apple besluttede at oprette sin egen M1-chip og integrere den i sine computere, indtil ARM virkelig er kommet ind i den indenlandske pc-industri.

Denne nye arkitektur, som ARM har kaldt DynamIQ (det er et ordspil på engelsk, der kombinerer ordet "dynamisk" med "IQ", IQ) er i princippet rettet mod mobile enheder og IoT enheder, men de har bekræftet, at de også har til hensigt at nå økosystemet med personlige computere og endda servere, da dets potentiale er enormt.

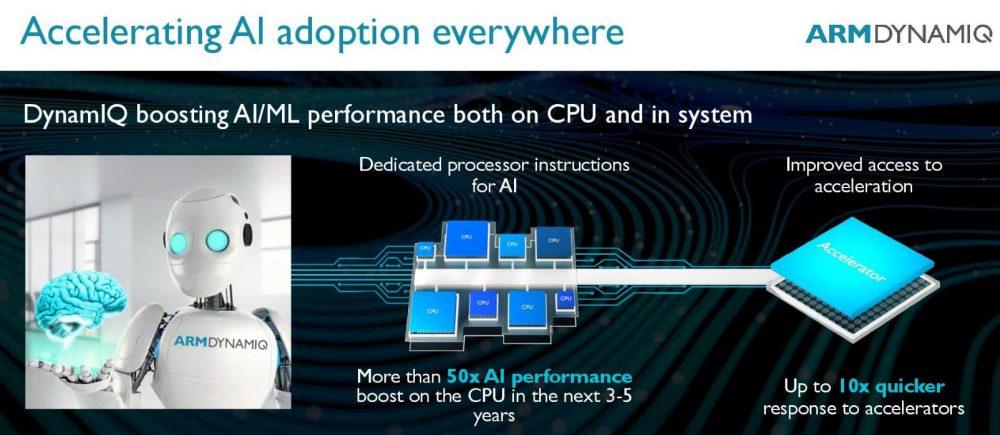

Ifølge ARM er formålet med denne arkitektur at gøre det muligt for deres chips at blive udstyret med virtual reality og machine learning-systemer, og til dette har de tilføjet flere kerner og et større antal instruktioner (og det er netop, hvad ARM har altid gjort "svag" sammenlignet med x86, da dens chips har meget mindre og mere specifikke instruktionssæt), der leverer op til 50 gange mere strøm samlet til AI-opgaver.

Det underliggende tema for DynamIQ er heterogen skalerbarhed; Disse to ord skjuler en masse jargon fra økosystemet, men da ARM forudsiger, at der vil blive solgt yderligere 100 milliarder ARM-chips i de næste 5 år, peger de på nøgleområder som bilindustrien, kunstig intelligens og maskinindlæring i den interessante ende af dette vækst. Som et resultat vil ydeevne, skalerbarhed og ventetid være nøgletal fremad, som DynamIQ har til hensigt at aktivere.

Et skridt ud over det store. LITTLE

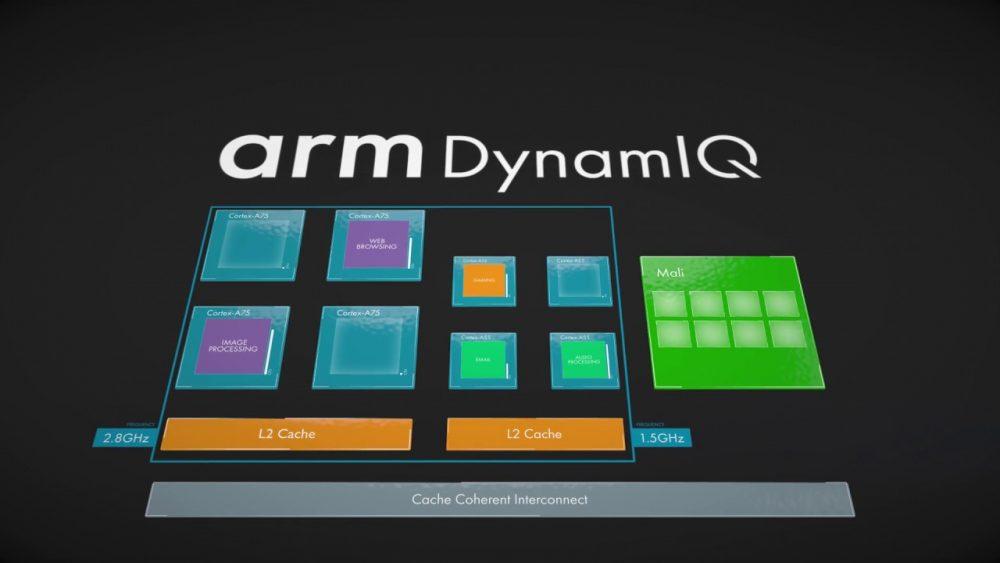

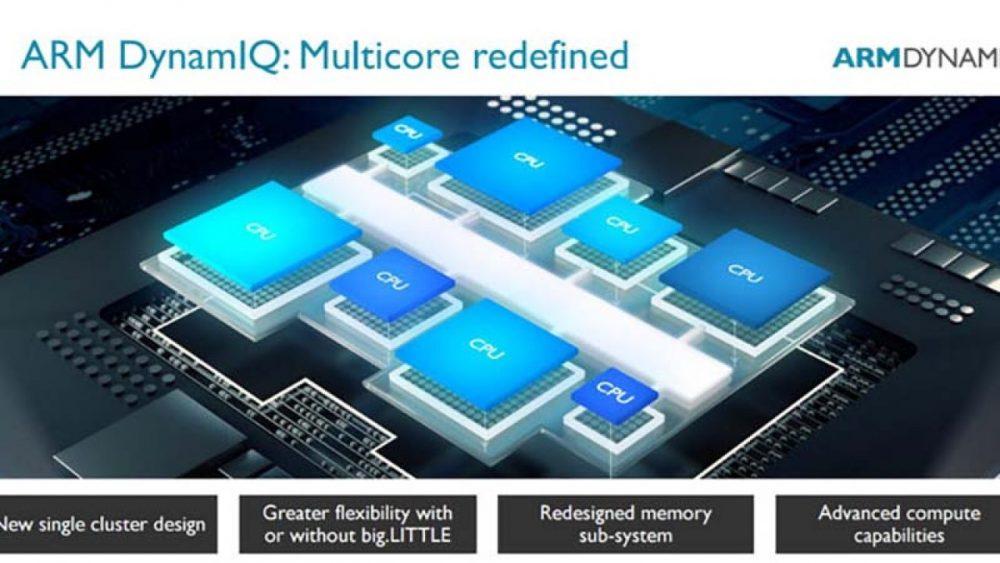

Den første fase af DynamIQ er et større klyngeparadigme, hvilket betyder op til otte kerner for hver af dem. Dette betyder imidlertid, at der også kan være et variabelt kerne design inden i en klynge; Disse otte kerner kunne være helt forskellige fra hinanden og endda fra forskellige Cortex-A-familier i forskellige konfigurationer.

Ligheden med big.LITTLE er mere end tydelig, kun at i stedet for at have "store kerner" og "små kerner", her ville det direkte give mulighed for at have et defineret antal kerner, og at hver af dem var forskellige fra alle kernerne . andre (dette er forskellen med big.LITTLE, virkelig).

Her opstår mange spørgsmål, såsom hvordan cachehierarkiet tillader tråde at migrere mellem kerner i en klynge (ligner måske hvordan tråde migrerer mellem big.LITTLE klynger i dag), selv når kernerne har forskellige cache-layout. ARM er ikke gået ind på dette detaljeringsniveau endnu, så det er stadig op i luften. Hver konfigurationsklynge med variabel kerne vil være en del af et nyt stof med yderligere strømbesparende tilstande, og dets mål er at give meget lavere ventetid.

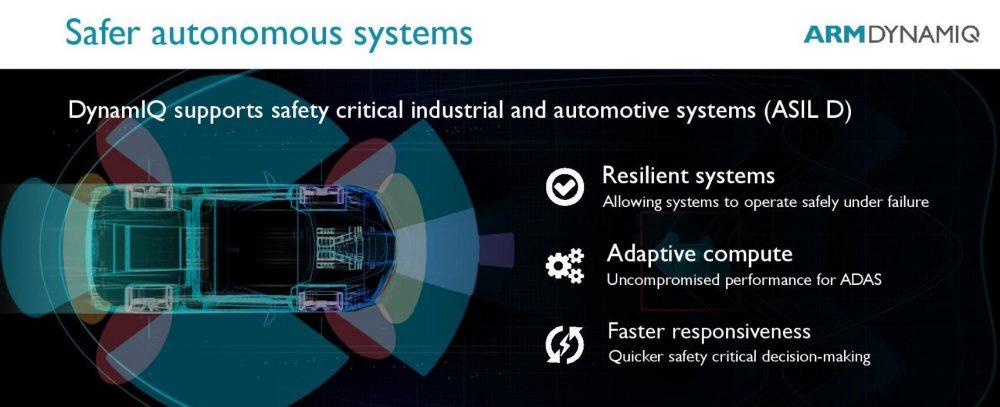

Det underliggende design tillader også, at hver kerne kan styres uafhængigt af spænding og frekvens samt strømbesparende søvntilstande. Ifølge de slides, der leveres af ARM, skal forskellige andre IP-blokke såsom acceleratorer være i stand til at oprette forbindelse til dette stof og drage fordel af den lave latenstid; genstande, der er citeret af ARM som sikkerhedskritiske bilbeslutninger, kunne i høj grad drage fordel af dette.

Et af ARMs vigtigste fokusområder er redundans. Den nye struktur gør det muligt at bruge et tilsyneladende ubegrænset antal klynger, så hvis en fejler, kan de andre tage plads. Når det er sagt, er den form for redundans, som nogle af ARM-chipkunder muligvis har brug for, failover i tilfælde af fysisk skade, som det kan ske i en autonom bilulykke. Det vil være interessant at se, om visionen om ARM med DynamIQ strækker sig til det niveau af redundans på SoC-niveauet, eller om denne type implementering afhænger af ARM-partnere.

Sammen med de nye rammer erklærede ARM, at et nyt design af hukommelsessystem er blevet implementeret for at hjælpe med beregningsfunktioner; dog nævnes intet specifikt. På den yderligere beregningslinje hævder ARM, at nye dedikerede processorinstruktioner (såsom begrænset præcision) til AI , Machine Learning vil integreres i en variant af ARMv8-arkitekturen.

Vi er ikke sikre i øjeblikket, om dette er en udvidelse til ARMv8.2-A, der introducerede medium præcision til databehandling, eller om det er en helt ny version. ARMv8.2-A tilføjer også RAS-funktioner og forbedringer af hukommelsesmodeller, hvilket er i overensstemmelse med det "nye hukommelsessystemsystem", der er nævnt ovenfor. ARM har sagt, at der er behov for nye kerner for at fremstille processorer med denne arkitektur.

Indtil videre er ARM DynamIQ fokuseret på nye og fremtidige teknologier som AI, bilindustrien og mixed reality, selvom det er korrekt, at det er klart, at DynamIQ kan bruges i andre eksisterende brugsmodeller som tablets, smartphones, pc'er og servere. Dette afhænger ja af, hvordan ARM gør det kompatibelt med nuværende kernedesign, da de simpelthen kunne frigive det som en separat licens.