Intel , AMD har annonceret brugen af 3DIC-teknologier af alle slags til at opbygge fremtidige processorer, en tendens, der vil vokse i de kommende år. Men hvordan kunne fremtidige Intel- og AMD-CPU'er bygget med denne teknologi? I denne artikel vil vi forsøge at kaste lys over, hvordan disse fremtidige processorer kan være.

Da nye fremstillingsnoder bruges, kan det ses, hvordan omkostningerne vokser mere og mere, hvilket tvinger ikke kun til at tage nye strategier med hensyn til design af nye processorer, men også nye måder at opbygge dem på.

Hvad forstår vi som 3DIC?

3DIC er akronymet for et tredimensionelt integreret kredsløb, som er navnet på alle processorer eller sæt af det samme, der består af flere forskellige chips, der er forbundet med hinanden ved hjælp af vias gennem silicium eller TSV. Indtil videre på markedet for pc-hardwarekomponenter har vi set 3D-NAND-hukommelsen fra forskellige mærker såvel som de forskellige generationer af HBM-hukommelse som kun demonstrationer

En af fordelene ved 3DIC er, at vi kan bruge flere chips med forskellige produktionsknudepunkter på en kombineret måde, dette er en fordel, fordi ikke alle elementerne i en processor skal skaleres til en ny produktionsknude, da de ikke giver en højere præstation for dem.

Direkte die-to-die eller hvordan man bygger en kompleks processor ved hjælp af 3DIC

Idéen om at forbinde to logiske chips en-til-en i en 3DIC-struktur ved hjælp af en lodret TSV-sammenkobling har potentialet til at ændre alle sektorer i processorbranchen fuldstændigt. Fra de meget lave SoC'er, der fungerer som den centrale processor i din telefon til high-end chips specialiseret i datacentre.

Ideen om at adskille en processor i to eller flere lodret justerede dele er noget, vi allerede har set i Intel Lakefield, hvor CPU kerner og Northbridge adskilles fra Southbridge på forskellige chips og anvender fremstillingsnoder. forskellige. Men vi skal begynde at se på nogle modeller af SoC'er og endda CPU'er.

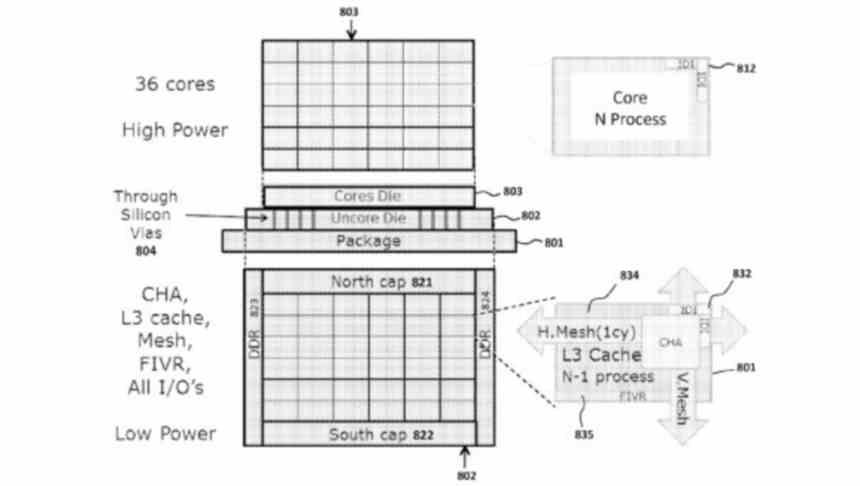

Men Intel-arkitektur er ikke den eneste måde at opbygge en moderne CPU ved hjælp af 3DIC-teknologi på, men der er også en anden type konfiguration, hvor CPU-kernerne og "uncore" fra den samme processor er adskilt i to eller flere forskellige chips, der er sammenkoblet via TSV.

Den største udfordring for CPU-arkitekter i øjeblikket er energiomkostningerne ved datatransmission i processoren, som i en konfiguration, vi taler om, er kraftigt reduceret, og derfor bliver 3DIC ikke kun Intel og AMDs fremtidige indsats, men det er også noget, som vi skal se i ARM verden.

En mulig fremtidig 3DIC-processor fra Intel eller AMD

For vores eksempel vil vi tage et eksempel på desktop-processorer baseret på Zen 2 og Zen 3, som deler kernerne i uncore, et element der også er kendt som Northbridge, selvom AMD kalder det Scalable Data Fabric. Vi skal bruge denne arkitektur, fordi den har en meget klar opdeling af komponenterne.

AMD, eller Intel, kunne frigive en fremtidig processor, hvor vi tilsyneladende ville se en monolitisk konfiguration, men virkelig være en 3DIC-processor, hvor uncore er på en anden chip i stakken end de forskellige kerner.

Dette ville betyde, at forbindelsen mellem CCD'erne eller Chiplets med SDF ikke kun ville være mere direkte og derfor med mindre ventetid, men også ville forbruge mindre takket være det faktum, at det ville være muligt for AMD eller Intel at bruge et større antal ben ved en lavere hastighed, men uden at miste båndbredde for at kommunikere de forskellige kerner med resten af processoren, hvilket igen vil gøre det muligt at øge ydeevnen pr. watt for de forskellige CPU'er betydeligt.

Ideen om at adskille processorer i flere niveauer vil tillade ting som at bygge multi-core-systemer, der går ud over 8 kerner på den samme chip og kommunikere dem alle sammen med en tilstrækkelig hastighed med god latenstid og forbruger meget lidt energi sammenlignet med nuværende modeller.

Hvilke handicap står Intel og AMD over for i implementeringen af 3DIC?

Den største afvejning er de enorme omkostninger ved at fremstille en 3DIC-processor, som kræver yderligere fremstillingstrin, men den største afvejning er det, der kaldes termisk stalling, som opstår, når to komponenter er så tæt, at temperaturen på en. det påvirker ydeevnen hos en anden og tillader ikke komponenter at nå de urhastigheder, som de kunne opnå separat og endda i en 3DIC-konfiguration.

Dette gør, at disse konfigurationer også kræver meget mere komplekse og dyre kølesystemer, som tilsammen tager dem væk fra hjemmesystemer og gør dem ideelle til servere af alle slags, men paradoksalt nok er de også fremtiden for SoC'er til PostPC-enheder.De er begrænsede i størrelse og kan ikke udvides mere vandret, så de kan kun gøre det lodret.

Årsagen til dette er, at med hver ny node øges ikke kun prisen for hver wafer-millimeter i kvadrat, men det bliver også stadig sværere at bygge større og større processorer uden en farlig fejlrate. Alt dette vil tvinge de fleste designs til at gå fra at være en enorm monolitisk chip til at bestå af flere lodrette chips, bare fordi prisen pr. Wafer vil være så høj, at selv de høje omkostninger ved 3DIC-fremstilling ikke vil være en hindring.