With the announcement this week of the first Apple Macintosh based on processors with ISA ARM, after having announced the transition by Apple a few months ago, the topic ARM vs x86 has appeared and the question of why there are no CPUs with ISA x86 on low-power devices it has reappeared. But what are the motives and myths surrounding this issue?

If you’ve ever wondered why you can’t see smartphones, tablets and all kinds of devices that use x86 processors with a consumption below 10 W and even 5 W. Then let us tell you that it is not due to lack of interest in Intel or AMD, but there are a number of reasons for this, a series of insurmountable barriers that have to do with the nature of the x86 architecture.

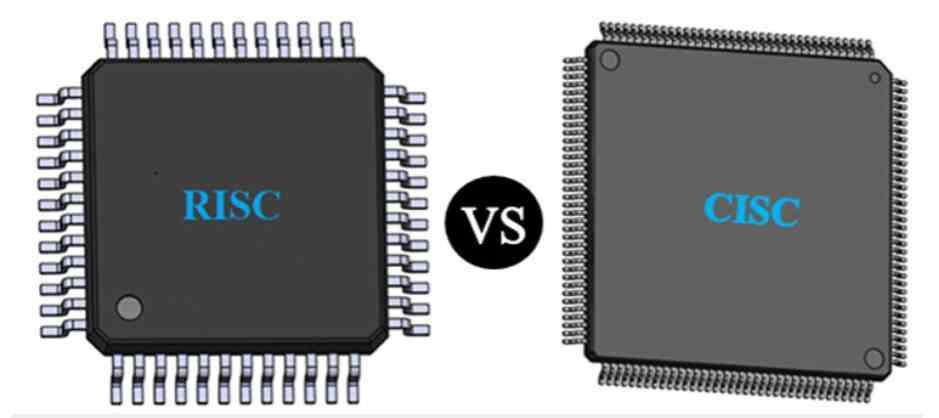

ARM vs x86 or CISC vs RISC

ARM stands for Advanced RISC Machines, while every x86-based CPU is said to have a CISC-like instruction set. But what does this mean? RISC stands for Reduced Instruction Set Computing or Computing with a Reduced Instruction Set, while CISC stands for Complex Instruction Set Computing, Therefore, it is a way of classifying the sets of instructions used by different processors.

The main difference is that because RISC has a reduced set of instructions, it ends up being necessary to use several simpler instructions to execute a more complex one, while in the case of a CISC unit many complex instructions can be carried out in a single instruction, so CISC drives save space in terms of the amount of memory.

For example, the machine code of a sum in RISC would be the following:

- Stores the first operand in the accumulator register

- Load the second operand and do the addition.

- Stores the result in the accumulator register.

Instead, on a CISC processor:

- Add the first and second operand.

As for machine code, a RISC binary has more instructions and therefore takes up much more memory , while in the CISC binary the code is much lighter.

The instruction cycle of processors

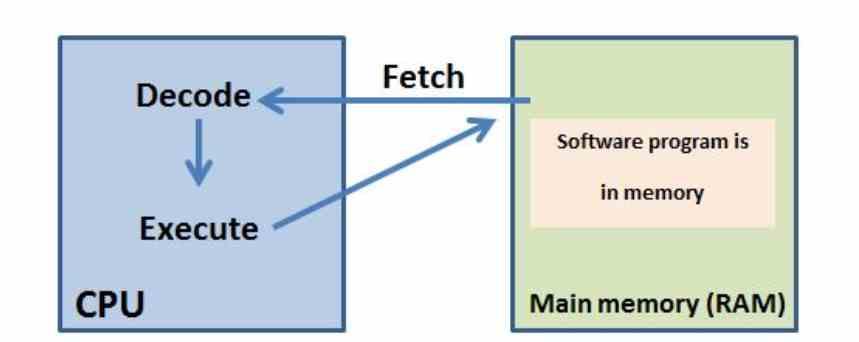

Every processor, regardless of whether it is CISC or RISC, has to go through four different stages which are:

• Fetch: The following instruction is fetched in memory.

• Decode: The instruction is decoded and prepared for execution.

• Execute: The instruction is executed by one of the execution units of the CPU. and the result of the instruction is written to the corresponding memory bank or register.

In RISC processors an instruction executed by the CPU is equivalent to an instruction in binary code, while in CISC an instruction in machine code can be broken down into several microinstructions, which means that the Decode unit of CISC processors is much more complex and is another of the most important factors for x86 to have a higher consumption.

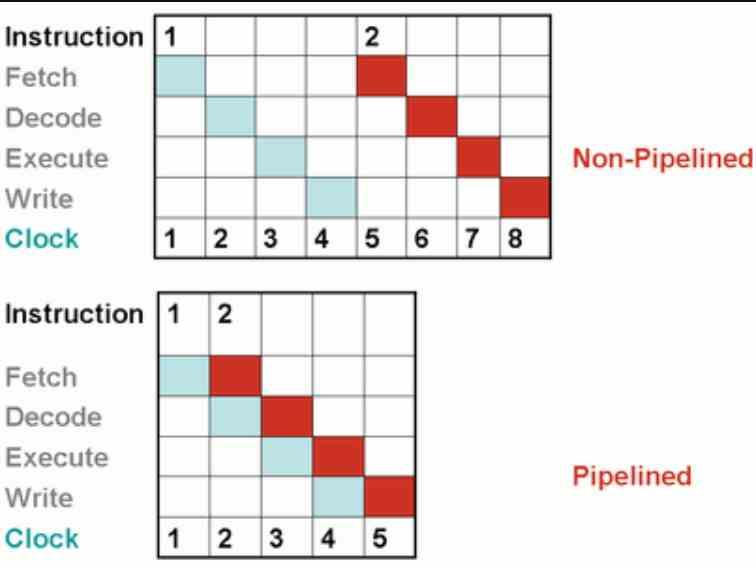

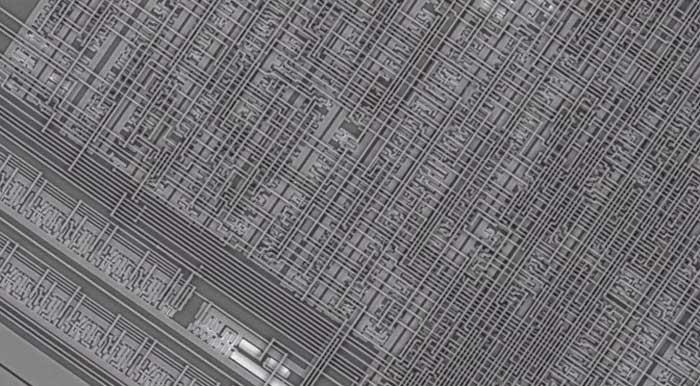

Segmentation on x86 vs ARM

One of the peculiarities that all CPUs have since the beginning of the 90s is segmentation, consisting in that instead of waiting for an instruction to be executed in full in the processor to make way for the next, these are advanced by each stage of the instruction cycle, which can be divided into several sub-stages each one of them.

Since RISC processors have a direct correlation between the number of instructions in the binary code and those executed by the CPU, it is very easy to segment the instructions into several stages. But in an x86 it is extremely difficult , since the segmentation is done on the microinstructions generated during the Decode stage, which means even more additional circuitry running and consuming power continuously.

Not only that, but while for example the opcodes of each instruction in ARM are of fixed size in the case of x86 they are variable, which makes the decoding of instructions in microinstructions much more complex in the case of x86 processors.

Fewer records equals less energy efficiency

The ISA x86 has much fewer registers inside it than other ISAS, this means that many instructions have to be carried out on the memory, or the caches, which causes that you end up consuming much more energy when executing. This is a classic problem of the x86 architecture and not because it is a CISC architecture.

To understand it, it is necessary to take into account the energy consumption of each operation depends on the distance between the data and the processor .

x86 vs ARM on very low power devices.

Intel tried it a few years ago with the failed Intel Medfield processor.

What’s more, one of the possibilities that have been considered is the creation of a mixed CPU , which consists of an x86 that internally decodes its instructions into ARM instructions and allows full compatibility between the two ISAS, which would be the definitive processor.

But sadly neither ARM nor Intel and AMD, especially the latter, are interested in making this mixed processor since to make it work in both modes it would be very difficult to achieve, apart from that the decoding of x86 instructions would continue to be a problem, so we would have a processor that could only work in one way and where most of the circuit would be wasted.