إذا كنت قد تابعت عالم المعالجات الدقيقة لبعض الوقت ، فإن الشيء الأكيد هو أنك ستكون على دراية بالاختصارات RISC و CISC ، والتي لا تعدو أن تكون تعريفًا لهيكل مجموعة التعليمات التي يتعامل معها المعالج. حسنًا ، في السنوات الأخيرة ظهر نموذج جديد أطلق عليه اسم VISC. مما تتكون؟

أصبحت معظم المعالجات الموجودة في السوق مملة ، لأنها تجلب القليل على الطاولة. إنها تستند إلى تحسين الأداء عن طريق ضبط الأجزاء الصغيرة بحيث يعمل الكل بشكل أفضل من ذي قبل ، ولكن في السنوات الأخيرة لم تكن هناك ثورة مثل تلك التي حدثت مع التنفيذ خارج النظام في منتصف التسعينيات ، ولكن هذا يمكن أن يتغير بفضل معماريات VISC ، التي تمثل نموذجًا جديدًا.

هل VISC عبارة عن مجموعة من التعليمات؟

أول ما قد يتبادر إلى الذهن عند قراءة هذه الاختصارات وبسبب تشابهها هو الكلمتان RISC و CISC اللتان تشيران إلى طبيعة مجموعة السجلات وتعليمات المعالج ، والتي ليست موضوع هذه المقالة ، حيث بموجب مفهوم VISC ، فإننا لا نشير إلى طريقة جديدة لتصنيف التعليمات ، ولكن إلى شيء مختلف تمامًا.

لفهم كيفية عمل نموذج VISC ، علينا أن نأخذ في الاعتبار مفهومين مختلفين بخصوص وحدة المعالجة المركزية: أداء. أولها حقيقة أن وحدات المعالجة المركزية للكمبيوتر الشخصي اليوم بها مجموعة تعليمات داخلية أصغر حتى من RISC ، لأن ما تفعله هو نقل كل تعليمات في تعليمات ميكروية أصغر داخليًا أثناء العملية. مرحلة فك التشفير. إذا كنا متطرفين ، فإن الاستنتاج اليوم لجميع المعالجات ليس أنهم من RISC ، ولكن لديهم مجموعة صغيرة جدًا من التعليمات التي تعمل داخليًا والتي تعمل على بناء بقية التعليمات. أي بمجرد وصول التعليمات إلى وحدة التحكم في وحدة المعالجة المركزية ، يتم تقسيمها إلى قائمة من الإرشادات.

لذا فقد فاز الأول بالحرب بين RISC و CISC ، ولكن مع الفخ الذي جعل x86 ، أكثر هندسة CISC استخدامًا ، فخ التصرف الداخلي مثل RISC. حتى يومنا هذا ما عدا ARMأما باقي أعضاء جهاز أمن المعلومات في عداد المفقودين أو على وشك الاختفاء. علاوة على ذلك ، حتى ARM قد تبنى مفهوم تقسيم التعليمات إلى تعليمات أبسط ، لذا فإن كلا النموذجين خارج تعريف ISA المشترك للعائلة قد انقرض بالفعل.

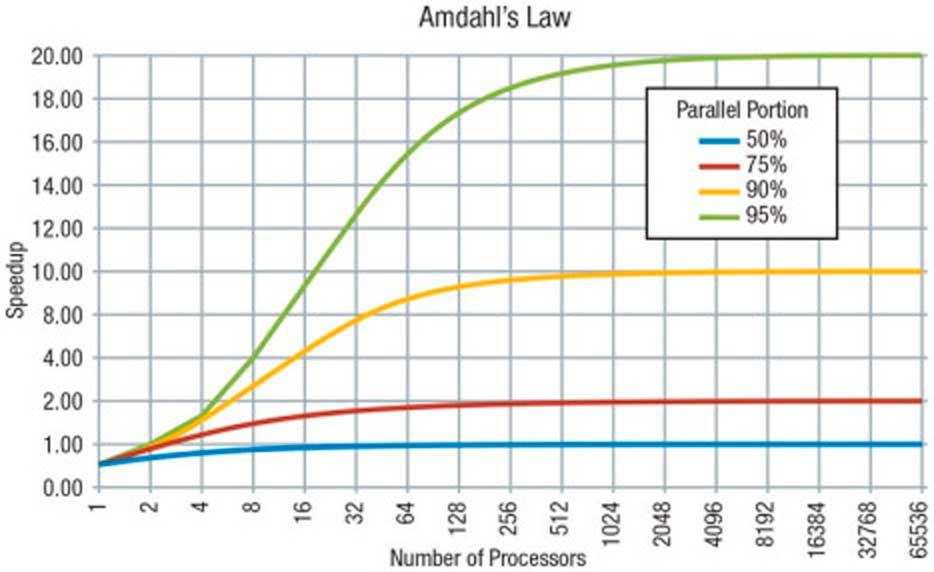

قانون أمدحل

لفهم البرنامج ، علينا أن نفهم أن البرنامج يتكون من جزأين مختلفين:

- الذي لا يمكن تنفيذه إلا في سلسلة ، وبالتالي لا يمكن حله إلا من خلال نواة واحدة عن طريق تنفيذ نواة تنفيذ منفرد.

- هذا الجزء من الكود يمكن تنفيذه بالتوازي ، مما يعني أنه يمكن حله بواسطة عدة مراكز في نفس الوقت وكلما زاد عددهم في المعالج ، كلما كان حل هذا الجزء أسرع.

إذا أخذنا في الاعتبار ما تم شرحه في القسم السابق ، فستستنتج أن بعض تعليمات المعالج التي تصبح رمزًا صغيرًا ما يفعلونه أصبحت سلسلة من الإرشادات التي يمكن أن تعمل في سلسلة أو بالتوازي بين عدة أنوية ، على الرغم من أن المعتاد هو أن معظم التعليمات يتم تنفيذها في نواة واحدة وأنه يتم تنفيذ التعليمات البرمجية بالتوازي عن طريق العناصر المشتركة.

لذلك ، فإن حقيقة أن جزءًا من الكود يتم تنفيذه بواسطة عدة مراكز يعتمد بشكل حصري على مطور البرنامج ، الذي يتعين عليه برمجته بشكل صريح بحيث تعمل أجزاء معينة بالتوازي.

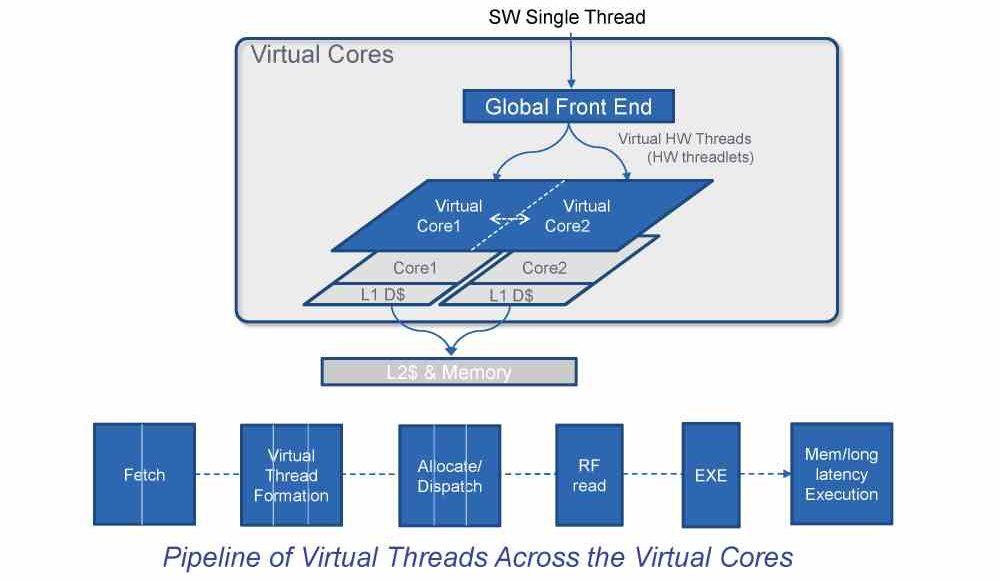

VISC والنوى الافتراضية

بمجرد شرح كل ما سبق ، يمكننا بعد ذلك شرح معنى الاختصار VISC ، والذي يكون تعريفه هو الإجابة المباشرة على السؤال التالي: عند إنشاء التعليمات الدقيقة في مرحلة فك التشفير ، ألا يمكنها العمل؟ بالتوازي مع عدة نوى بدلاً من القيام بذلك في نفس الشيء؟

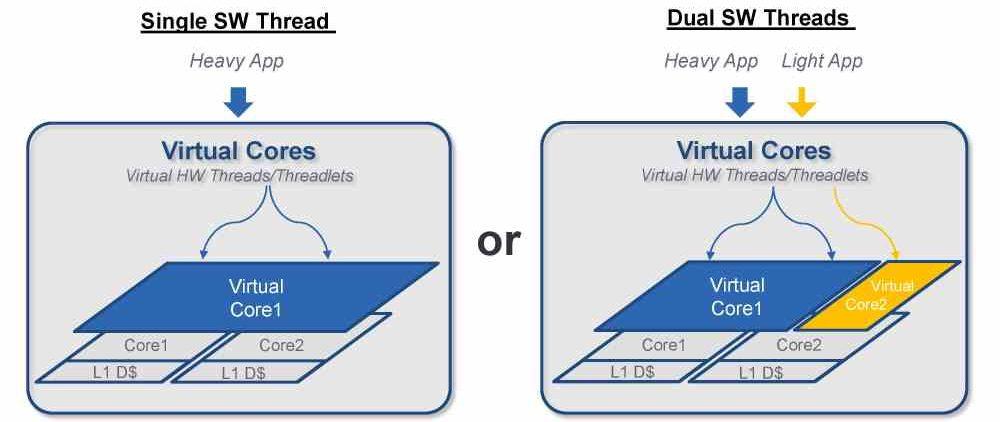

حسنًا ، الإجابة على السؤال حول بنية VISC ، التي أثيرت لأول مرة من قبل شركة تسمى Soft Machines في عام 2015 كمفهوم لتحسين أداء وحدة المعالجة المركزية. تم شراء هذه الشركة الناشئة الصغيرة بواسطة إنتل في عام 2016 وقد عملوا على تطوير بنية VISC منذ ذلك الحين. كيف يعمل؟ حسنًا ، يمكن تعريفه بسهولة شديدة: يتم إرسال سلسلة تنفيذ واحدة إلى الواجهة الأمامية العالمية للمعالج ، والتي يتم تحويلها إلى العديد من المهام التي تؤدي نفس الوظيفة وتعمل بشكل متوازٍ وتعمل في مراكز افتراضية. يتم تنفيذ عملية التحويل على مستوى البرنامج من خلال طبقة ترجمة ، ولكن يجب أن نضع في اعتبارنا أن هذا يمكن أن يكون شيئًا بسيطًا مثل متحكم ينفذ نقل التعليمات.

على عكس ما يحدث في توزيع المهام في معالج تقليدي متعدد النواة ، في بنية VISC ، ليس المقصود أن يكون النواة حرة في تنفيذ التعليمات ، ولكن العناصر اللازمة لتنفيذه متوفرة داخل المعالج لتنفيذه. على سبيل المثال ، قد يحدث أنه في النواة التقليدية لا يتم استخدام وحدة المتجه ، ولكن في ظل هذا النموذج يمكن استخدامها لتشكيل أحد التعليمات.

VISC والأداء

عند اعتماد نموذج جديد فيما يتعلق بالهندسة المعمارية ، فإن أول شيء يجب مراعاته هو كيفية تأثيره على الأداء ، لأنه لا يستحق تغيير النموذج الحالي إذا لم ينتج عنه زيادة في أداء المعالج بشكل عام. الطريقة الأكثر كلاسيكية لزيادة أداء المعالج هي زيادة عدد التعليمات التي يتم حلها في كل دورة على مدار الساعة ، وهذا يعني زيادة تعقيد الأجهزة ، نظرًا لحقيقة أن إضافة النوى يجب أن نحسب كل البنية التحتية التي يحيط بهم يصبح هو نفسه أو أكثر تعقيدًا.

ما يميز VISC عن الباقي هو توزيع موارد المعالج لتنفيذ التعليمات المختلفة في بضع دورات على مدار الساعة ، بين 1 و 4 مراكز. بهذه الطريقة ، إذا كانت هناك تعليمتان تتنافسان على موارد أخرى في نواة ، فيمكن إعادة تخصيصهما بسرعة كبيرة لجزء آخر من المعالج حيث تتوفر هذه الموارد نفسها.

النموذج الحالي ، وهو التنفيذ خارج الترتيب ، ما يفعله هو إعادة ترتيب تنفيذ التعليمات وفقًا للموارد المجانية في جميع الأوقات ثم إعادة ترتيب إخراج البيانات التي تمت معالجتها بالفعل. القيد؟ يتم تنفيذ تخصيص الموارد على مستوى النواة الواحدة بدلاً من المستوى متعدد النواة ، وهذا هو المفتاح لأداء أعلى لهياكل VISC.

هل هذه المعالجات موجودة اليوم؟

على الرغم من أن المفهوم جيد جدًا على الورق ، إلا أنه لم يقدم أحد حتى الآن معالجًا يعمل وفقًا لهذا النموذج ، ولكن نظرًا لأننا نقترب تدريجياً من حدود النموذج الحالي ، فمن المهم أن نضع في الاعتبار أن هناك حلول يمكن أن تخدم لتحسين أداء وحدة المعالجة المركزية لأجهزة الكمبيوتر الخاصة بنا في المستقبل.

إن امتلاك معالج أكثر قوة لا يعني فقط الحصول على معالج أسرع أو بعدد أكبر من النوى ، ولكنه يعتمد على معرفة كيفية الاستفادة من الموارد المتاحة. كان التنفيذ خارج النظام هو الخطوة الأولى بهذا المعنى ، ولكن منذ ذلك الحين كانت التغييرات طفيفة بشكل عام خارج نطاق الذهاب إلى متعدد الأنوية. لا يزال VISC مفهومًا ، ولكنه ليس مستحيلًا وهو وسيلة للاستفادة من الموارد المتاحة في المعالج بطريقة أكثر كفاءة.

نحن نعلم حتى الآن أن هذا المفهوم ممكن في وحدة المعالجة المركزية منذ أن صممت Soft Machines وصنعت واحدًا باستخدام هذا النموذج ، لذلك على الرغم من أنه كان على مستوى تجريبي ، فإننا نعلم أنه من الممكن تنفيذ مثل هذا التصميم. شيء آخر مختلف هو صعوبة إحضار المجموعة الكاملة من تعليمات وسجلات x86 إلى هذا النموذج ، وهو معقد للغاية بطبيعته.