في السنوات القادمة ، ستصبح عقدة N5 لأكبر مسبك آسيوي أهم عقد تصنيع في السنوات القادمة. حسنًا ، من خلال تحليل إحدى الرقائق المصنعة بالفعل بموجب عملية التصنيع المذكورة ، تم اكتشاف ذلك كثافة عقدة TSMC 5nm أقل من المتوقع . هل هذا خبر سيء أم عدم صدق من جانبك؟

سوف تصبح عقدة TSMC 5nm ومتغيراتها الأكثر صلة في السنوات القادمة داخل جهاز الكمبيوتر. ليس فقط بسبب حقيقة ذلك AMD ستستخدمه في رقائقه المستقبلية مثل Ryzen 7000 و EPYC Genoa ووحدات معالجة الرسومات RX 7000. ولا يمكننا أن ننسى أن TSMC هي أيضًا عميل وحتى إنتل، نظرًا لأن الرسومات المدمجة في Meteor Lake وبعض مكونات رسومات Ponte Vecchio HPC ستستخدمها في التصنيع. لذلك ، بطريقة أو بأخرى ، يستفيد اللاعبون الرئيسيون في الصناعة من عقدة التصنيع هذه بطريقة أو بأخرى. على الرغم من أنه في الوقت الحالي ، فإن الرقائق الوحيدة التي تستخدم عملية التصنيع هذه هي تلك الخاصة بـ تفاح

كثافة عقدة TSMC 5nm أقل من المعلن عنها

على الرغم من أن هذا العنوان قد يبدو سلبيًا ، إلا أن هذا له تفسير وهو أنه من Angstronomics قاموا بعمل مقال مثير للاهتمام حيث أبلغونا عن سبب إعطاء TSMC كثافة العقدة 5nm بشكل خاطئ. ونعني بهذا عدد الترانزستورات لكل منطقة وبالتالي مدى تعقيد بناء الرقائق. يذكر المسبك التايواني رسميًا أنه يبلغ 171 مليون ترانزستور لكل مليمتر مربع . ومع ذلك ، يكشف التحليل الشامل أن هذا الرقم أقل وأنه كذلك 137.6 مليون ترانزستور لكل مليمتر مربع .

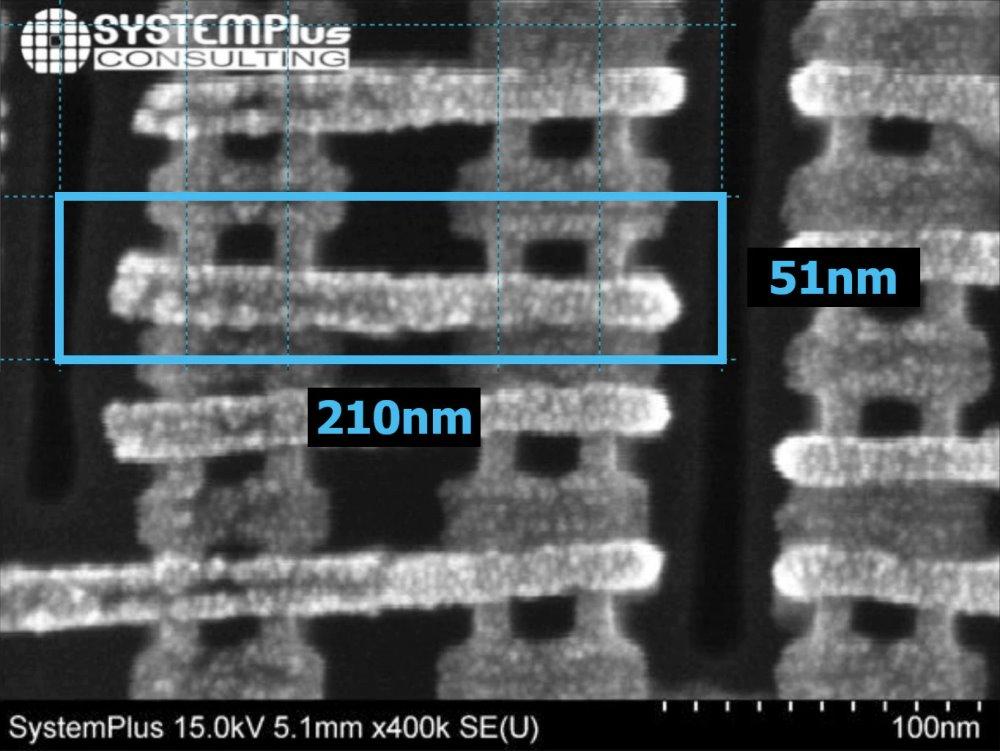

وقد فعلوا ذلك عن طريق قياس حجم الترانزستورات المستخدمة في بناء معالج Apple A15 من أحدث جيل من خلال مجهر إلكتروني. اي فون. والتي تقيس 210 نانومتر في ارتفاع الخلية و 51 نانومتر في CPP . حسنًا ، يتم استخدام كلتا القيمتين بطريقة مقارنة لمعرفة حجم الترانزستور فيما يتعلق بالعقدة السابقة. وبالتالي ، فإن عقدة TSMC N7 لها قيم 240 نانومتر و 57 نانومتر على التوالي ، مما يمنحها كثافة 90.64 مليون ترانزستور لكل مليمتر مربع . في حالة عقدة Intel مقاس 10 مم ، والتي تم تسميتها مؤخرًا Intel 7 ، فإننا نتحدث عن رقم 100.33

إذا كانت الأرقام تصيبك بالدوار ، فلا داعي للقلق. هذا يعني أنه في نفس المساحة يمكن لمصممي الرقائق أن يصلوا إلى 51.8٪ بوابات منطقية أكثر على الرقائق المصنعة 5 نانومتر مقارنة بالرقائق 7 نانومتر . مما يعني أنها ليست قفزة عقدة كاملة. في الواقع الترانزستورات ليست حتى 5 نانومتر. منذ أن توقف هذا المقياس عن التوافق مع الواقع منذ وقت طويل وأصبح أكثر من أداة تسويقية.

هل أعطى TSMC أرقامًا كاذبة؟

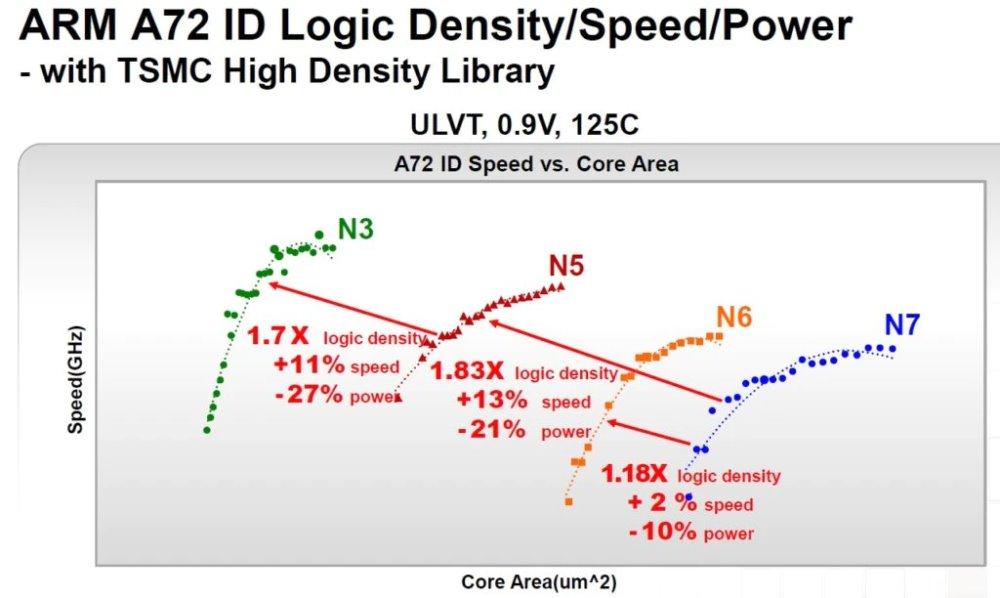

لا ، ليس حقًا ، وذلك لأن المسبك التايواني لا يستخدم المقياس الذي ناقشناه في القسم السابق. ما يفعله TSMC عادةً هو تكييف شريحة معروفة بالفعل مع العقدة الجديدة للحصول على مقاييسها. لهذا الغرض ، يستخدمون تصميم Cortex A72 ، بالطبع ، نظرًا لأنه تصميم رائع ، يتمتع المسبك بكل الحرية في العالم عندما يتعلق الأمر باستخدام نوع واحد من الترانزستور أو آخر لبناء منطق مختلف البوابات المكونة للرقاقة.

لذا ، كما ترون في الصورة فوق هذه السطور ، يمكننا أن نستنتج من أين تحصل TSMC على أرقامها . وهي تشير فقط إلى كثافة المنطق. لذلك تم استبعاد SRAM أو الأجزاء التناظرية من الشريحة ، على سبيل المثال. بالمناسبة ، يمكن ملاحظة كيف أن الانتقال من العقد الحالية إلى العقد المستقبلية لا يؤدي إلى توفير كبير في الاستهلاك أو زيادة مهمة في السرعة. وهو ما يفسر جزئيًا الاستهلاك المتزايد للنماذج المتطورة للجيل القادم من بطاقات الرسومات من NVIDIA و AMD.

على أي حال ، هذا لا يؤثر على أي من شركاء المسبك والرقائق المستقبلية التي سيتم تصنيعها فيه. انتهى العديد منهم بالفعل ويوشكون على الطباعة على رقائقهم على نطاق واسع.