إذا كنت قد تساءلت يومًا ما هي العملية التي يتبعها المعالج و رامات التي كلفتها بالحصول على البيانات والتعليمات التي يتعين عليها تنفيذها ، فأنت محظوظ ، لأننا في هذه المقالة سنشرح كيف تتواصل عملية الاتصال هذه بين أهم عنصرين في جهاز الكمبيوتر مع كل منهما آخر.

في هذه المقالة لن نشرح أي نوع من ذاكرة الوصول العشوائي أفضل or مواصفات كل واحد ، لكن المعالج يتواصل معها ليتمكن من تنفيذ البرامج.

السبب نستخدم ذاكرة خارجية لأن كمية الترانزستورات اللازمة لتخزين المعلومات لن تتناسب مع مساحة المعالج ، لذلك من الضروري استخدام ذاكرة الوصول العشوائي خارج المعالج لتخزين التعليمات والبيانات التي سيتم تشغيلها.

لماذا يحتاج المعالج إلى اتصال مع ذاكرة الوصول العشوائي؟

المرحلة التي فيها وحدة المعالجة المركزية: تأخذ التعليمات التالية لتنفيذه من ذاكرة الوصول العشوائي تسمى "الجلب" وهي واحدة من المراحل الثلاث التي تشكل دورة التعليمات: الجلب-فك الشفرة-التنفيذ ، والتي سنتحدث عنها فقط في هذه المقالة من الأولى ، بينما الأخرى سيتم ترك اثنين لمرة أخرى لأن ذاكرة RAM لا تتدخل فيها ، إلا لكتابة النتيجة مرة أخرى.

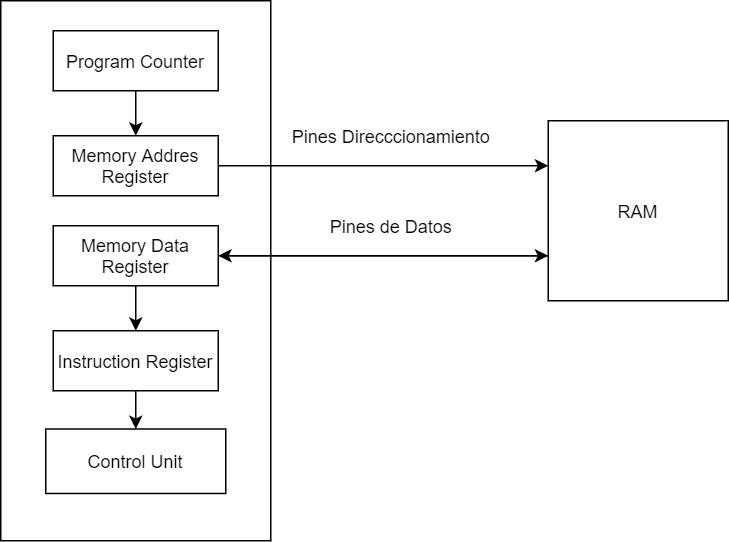

يحتوي كل معالج على سلسلة من السجلات المتصلة ببعضها البعض والتي تعمل على التقاط التعليمات التالية ، وهي كالتالي:

- عداد البرنامج: يشير الكمبيوتر الشخصي إلى سطر الذاكرة التالي حيث توجد تعليمات المعالج التالية. يتم زيادة قيمته بمقدار 1 في كل مرة يتم فيها إكمال دورة التعليمات الكاملة أو عندما يغير تعليمة القفز قيمة عداد البرنامج.

- تسجيل عنوان الذاكرة: يقوم MAR بنسخ محتوى جهاز الكمبيوتر وإرساله إلى ذاكرة الوصول العشوائي من خلال دبابيس عنوان وحدة المعالجة المركزية ، والتي تكون سلكية مع دبابيس عنوان ذاكرة الوصول العشوائي.

- تسجيل بيانات الذاكرة : إذا تمت قراءة التعليمات ، فإن ذاكرة الوصول العشوائي ستنقل عبر ناقل البيانات محتوى عنوان الذاكرة الذي كان يشير إليه MAR.

- تعليمات التسجيل: يتم نسخ التعليمات إلى سجل التعليمات ، حيث ستقوم وحدة التحكم بفك تشفيرها لمعرفة كيفية تنفيذ التعليمات.

ما هي ذاكرة DRAM؟

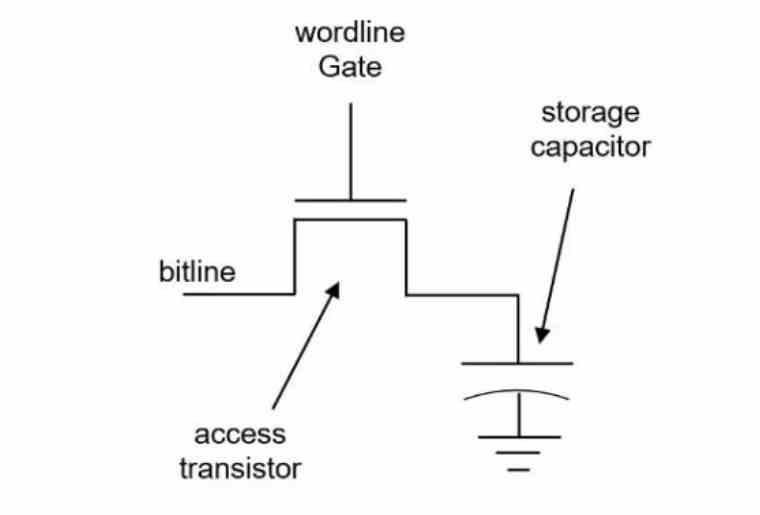

• نوع الذاكرة المستخدمة لذاكرة الوصول العشوائي ، مثل ذاكرة الوصول العشوائي للنظام وذاكرة الوصول العشوائي للفيديو أو VRAM ذاكرة DRAM أو 1T-DRAM . في هذا النوع من الذاكرة يتم تخزين كل بت في ملف مزيج من مكثف وترانزستور ، بدلاً من العديد من الترانزستورات مثل SRAM ، ومن هنا جاء اسم 1T-DRAM.

جميع ذاكرة الوصول العشوائي (RAM) المستخدمة حاليًا في الكمبيوتر: DDR4 ، GDDR6 ، HBM2e ، LPDDR4 ، إلخ. إنها ذكريات من نوع DRAM ، في حين أن الذكريات الداخلية للمعالجات ، وذاكرة التخزين المؤقت للتسجيل ، ولوحات التخزين من نوع SRAM.

المجموعة المذكورة من مكثف وترانزستور تسمى أ بتسيل , عندما يتم شحن مكثف خلية البت ، يتم تفسير أن المعلومات الموجودة في خلية البت هذه هي 1 ، عندما لا يتم شحنها ، يتم تفسيرها على أنها 0.

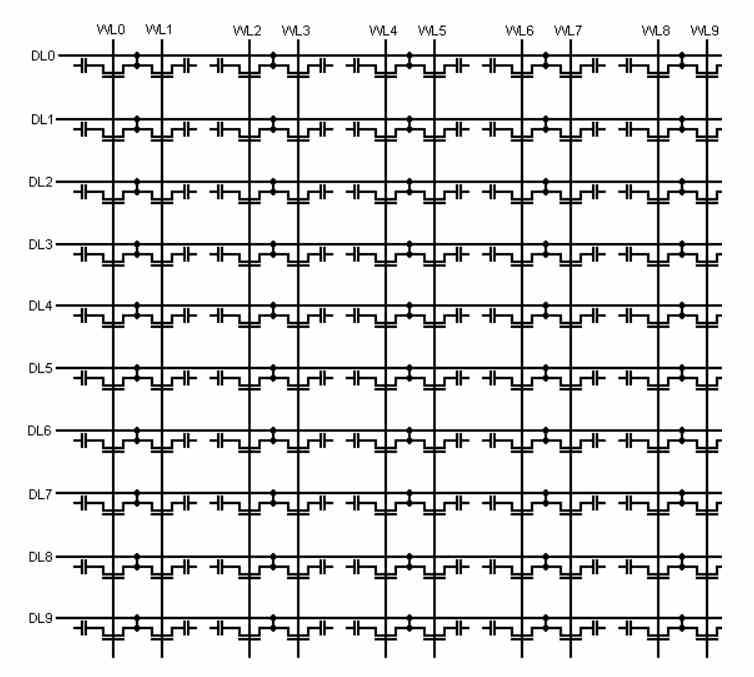

يتم تنظيم خلايا البت في مصفوفة حيث يتم استخدام دبابيس العنونة للوصول إليها على النحو التالي:

- يحدد النصف الأول من البتات الصف الذي نريد الوصول إليه

- يحتوي النصف الثاني من وحدات بت العنونة على العمود الذي نريد الوصول إليه ،

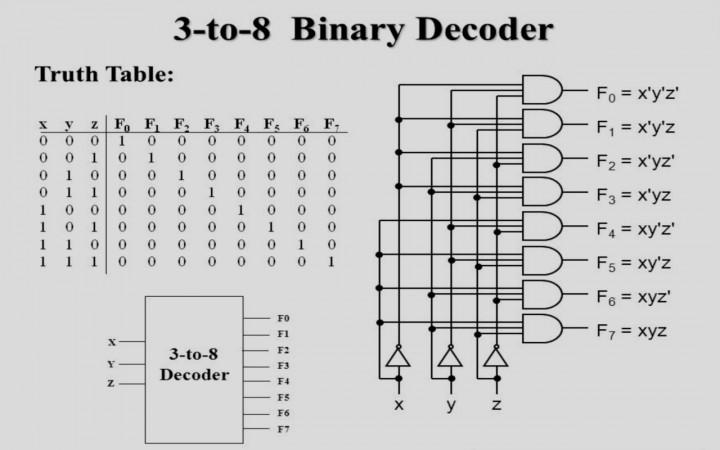

لهذا ، يوجد مفكك تشفير ثنائي بين مصفوفة خلايا البت وناقل العنونة الذي يسمح باختيار خلية البت المناسبة.

دبابيس الاتصال للتواصل مع ذاكرة الوصول العشوائي

للوصول إلى ذاكرة الوصول العشوائي ، تستخدم وحدة المعالجة المركزية سلسلة من المسامير التي تسمح لها بالوصول إلى محتويات ملف رامات وحتى تعديله . للقيام بذلك ، تحتاج أولاً إلى تحديد مكان البيانات أو أين نريد معالجتها ، ثم نقلها في اتجاه معين. يتم استخدام نوعين مختلفين من المسامير لهذا الغرض.

- معالجة دبابيس : عادةً ما يتم تمييزه من A0 إلى AN ، حيث N هو عدد الدبابيس ويساوي عدد بتات العنونة ، والتي تكون دائمًا 2 ^ N.

- دبابيس البيانات : حيث يتم نقل البيانات من وإلى ذاكرة الوصول العشوائي.

- تمكين الكتابة: إذا كان الدبوس نشطًا ، فسيتم نقل البيانات نحو الذاكرة ، والكتابة ، من ناحية أخرى ، إذا لم يكن نشطًا ، يتم ذلك تجاه المعالج ، القراءة.

إذا كان نظامنا يحتوي على العديد من شرائح ذاكرة RAM ، فسيتم استخدام البتات الأولى من العنوان لتحديد أي من شرائح الذاكرة التي نريد الوصول إليها داخل وحدة ذاكرة DIMM. كانت هناك أيضًا حالات يكون فيها العنوان ودبابيس البيانات متماثلين. هذا يرجع إلى حقيقة أن العنونة والوصول إلى البيانات لا يتم في وقت واحد.

ولكن لفهم كيفية عمل العنونة بشكل أكثر دقة ، يتعين علينا مراجعة قطعة أساسية من الإلكترونيات ، وهي وحدة فك التشفير الثنائية.

وحدة فك التشفير الثنائية ودورها في التواصل مع RAM

مفكك التشفير الثنائي هو جزء شائع جدًا من الإلكترونيات ، ويتكون من ذلك من إدخال n بت ، يتم اختيار الإدخال من 2 ^ n احتمالات مختلفة. تم بناؤه عن طريق وضع n NOT بوابات على بوابات 2 ^ n AND.

مفكك التشفير الثنائي هو جزء شائع جدًا من الإلكترونيات ، ويتكون من ذلك من إدخال n بت ، يتم اختيار الإدخال من 2 ^ n احتمالات مختلفة. تم بناؤه عن طريق وضع n NOT بوابات على بوابات 2 ^ n AND.

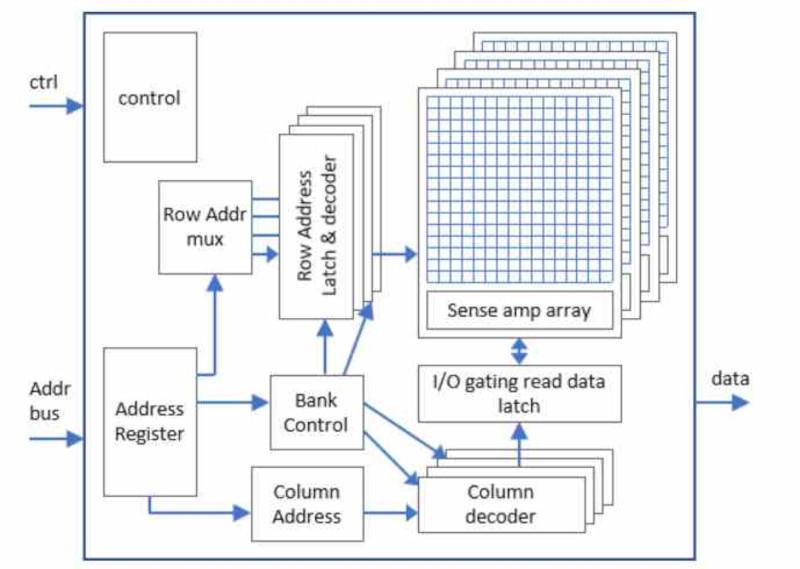

في ذاكرة RAM ، يتم إرسال العنونة على دورتين: يتم إرسال الصف المراد الوصول إليه أولاً ثم العمود ، بدلاً من إرساله في وقت واحد.

السبب في ذلك له تفسير بسيط للغاية: تخيل أن لديك معالجًا به 16 بت عنونة متصلة بشريحة ذاكرة RAM واحدة. إذا كانت وحدة فك التشفير الثنائية 16 بت ، فستكون هناك حاجة إلى 16 بوابة وليس 65536 وبوابات. في المقابل ، يحتوي جهاز فك التشفير الثنائي 8 بت على 8 بوابات و 256 بوابة ، وهو أسهل بكثير في التنفيذ.

هذا هو السبب في أن معالجة RAM تتم على مرحلتين.

بنوك الذاكرة

البيانات الموجودة في ذاكرة الوصول العشوائي لا يتم تخزينها على التوالي ، ولكن في بنوك مختلفة داخل نفس الشريحة ، كل بنك يحتوي على مجموعة من bitcells ، ولكن إذا أردنا على سبيل المثال إرسال عدد n من البيانات ، فسنحتاج إلى عدد n من مصفوفات bitcells حيث يتم توصيل كل واحدة منها بدبوس في ناقل البيانات.

استخدام بنوك متعددة ، في نفس شريحة الذاكرة ، يسمح بتحديد عدة وحدات بت في نفس الوقت مع وصول واحد إلى الذاكرة ، منذ تشترك جميع البنوك في العنوان . لذلك إذا كان لدينا 8 بنوك ذاكرة ، فإن اختيار bitcell معين سينتهي به الأمر إلى نقل البيانات من وإلى 8 بنوك ذاكرة في نفس الوقت.

الحجم القياسي للبنوك في ذاكرات RAM هو 8 بت ، وبالتالي فإن الحد الأقصى للذاكرة في العنونة يُحسب دائمًا على أنه 2 ^ ن بايت. في الواقع ، الحافلات ذات 16 ، 32 ، 64 بت ، إلخ. ما يفعلونه هو نقل بيانات العديد من عناوين الذاكرة المتتالية بدءًا من الأول.

الاتصال بين ذاكرة الوصول العشوائي ووحدة المعالجة المركزية

يعتمد الاتصال بين وحدة المعالجة المركزية وذاكرة الوصول العشوائي على أنه يتم بشكل صحيح ، أي أن البيانات الصحيحة يتم إرسالها ، في الاتجاه الصحيح وفي بنك الذاكرة الصحيح. لذلك ، كل ذاكرة RAM لديها نافذة فرصة ، وهي الوقت الذي يمكن فيه تنفيذ العمليات المختلفة ، يجب تنفيذها في أوقات محددة واتباع هذه العملية:

- حدد العمود (العنونة)

- حدد الصف (عنونة)

- نقل البيانات.

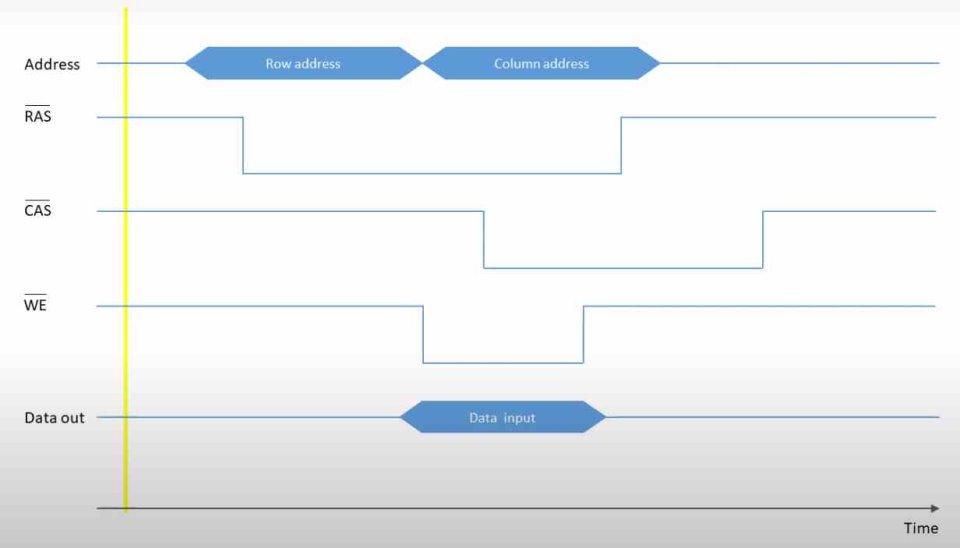

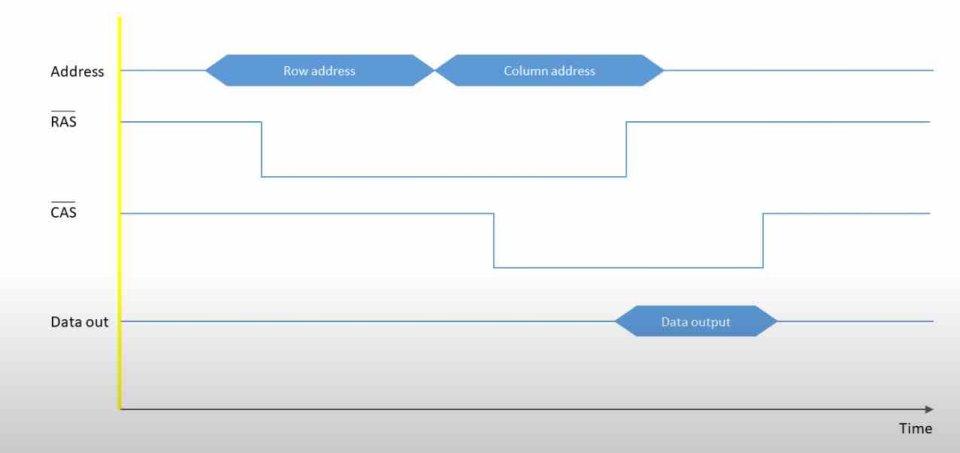

لهذا الغرض ، يتم استخدام سلسلة من المسامير الخاصة ، أحدها رأيناه بالفعل وهو خاصية Write Enable ، لكن الاثنين الآخرين هما التاليان:

- ستروب الوصول إلى العمود: يتم تنشيط هذا الدبوس عندما نشير إلى ذاكرة RAM بأننا نشير إلى العمود الذي نريد الوصول إليه.

- ستروب الوصول إلى الصف :: يتم تنشيط هذا الدبوس عندما نشير إلى ذاكرة RAM التي نشير إلى الصف الذي نريد الوصول إليه.

يمكن تلخيص كلتا العمليتين على النحو التالي:

- عملية القراءة بسيطة جدًا ، لذلك يجب أن يكون دبوس WE غير نشط ، للإشارة إلى أن البيانات تنتقل من ذاكرة الوصول العشوائي إلى المعالج ، وتشير إلى الصف ثم العمود حتى تتدفق المعلومات نحو المعالج من ذاكرة الوصول العشوائي .

- تختلف عملية الكتابة إلى حد ما ، لذلك يجب أن يكون دبوس WE نشطًا ، ولكن لا يتم نقل البيانات بعد تحديد عمود البيانات ولكن بمجرد تحديد الصف وفي نفس الوقت مع تحديد العمود حيث توجد البيانات.

باستخدام هذا ، يمكنك بالفعل الحصول على فكرة تقريبية عن كيفية عمل الاتصال بين المعالج وذاكرة الوصول العشوائي الخاصة به.