يستهدف السوق أجهزة chiplets ، أو هكذا يبدو. AMD كان مع الترتيب القائم على MCM لعدة سنوات حتى الآن و إنتل على وشك اتخاذ الخطوة التالية مع تقنيات مثل Foveros ، ولكن هل هذه خطوة يجب مشاهدتها؟ نحن نعلم بالفعل مزاياها وعيوبها؟ سنرى اليوم الخير والشر في chiplets ولماذا لا ترى الصناعة هذه الطريقة في إنشاء وحدات المعالجة المركزية بشكل واضح.

جميع كبرى منها AMD و Intel و TSMC و Marvell تعمل على مقاربات مختلفة لعالم chiplets ، بدائل مختلفة تحاول تطوير تصميمات أكثر تقدمًا. على الرغم من أننا تناولنا في المقالات السابقة هذا الموضوع المحدد ، إلا أن هناك نقاطًا معينة نتركها لهذه المناسبة ، نظرًا لأن الصناعة ليست متأكدة من أن chiplets هي الطريق الصحيح.

عدم وجود النظام البيئي والمعايير والوقت وتكاليف التنمية

ليس كل ما يلمع هو الذهب ، وعلى الرغم من أن AMD هي واحدة من القلائل الذين يطلقون منتجات حقيقية في السوق على أساس شرائح صغيرة ، إلا أنه ليس من السهل تمامًا القيام بذلك. تكمن المشكلة في عدم وجود نظام بيئي ، ولا توجد معايير ثابتة يمكن للصناعة اتباعها لتقليل أوقات الإنشاء وتكاليف التطوير.

تواجه كل شركة ، بشكل أو بآخر ، مشاكلها بشكل فردي ، وحدوي ، ولكن لا يوجد لدى كل منها بشكل منفصل كل القطع لتشكيل اللغز. بدلاً من ذلك ، وبشكل غريب ، يواجه جميعهم تقريبًا نفس المشاكل:

- إنهم يحاولون تقديم شيبس أمثل مع اتصالات أفضل وأسرع يمكن أن تتوسع إلى منتجات مختلفة.

- إنهم بحاجة إلى تقنيات تابعة لجهات خارجية إلى حد أكبر أو أقل.

- عدم وجود دعم في تصاميم مخططات التوصيل البيني بين القوالب.

- إنهم بحاجة إلى عناوين IP الصحيحة مع قدرات التصنيع.

هذا يتسبب ، على سبيل المثال ، في أن تتبع Intel مسارها استنادًا إلى monodie لوحدات المعالجة المركزية ، وهو أمر سنراه لسنوات قليلة. كانت AMD رائدة ، لكنها تدفع تكاليف كبيرة لأنها تعتمد على أطراف ثالثة وهذه بدورها شركات متخصصة لتقنيات معينة يجب تطويرها حصريًا ، مما يزيد من التكاليف الإجمالية.

هناك حاجة إلى أدوات EDA للانضمام إلى جميع هذه القطع ، نظرًا لأنها هياكل ومنتجات مختلفة وواجهات مادية ومنطقية للانضمام وتصنيف المعلومات من شركات مختلفة لإطلاق منتج واحد. أيضا ، قد لا تكون بعض المكونات الرئيسية متاحة على هذا النحو ، مما يؤدي إلى تفاقم المشكلة.

يجب على الصناعة مشاركة عناوين IP مختلفة إذا كانت ترغب في المضي قدمًا مع chiplets

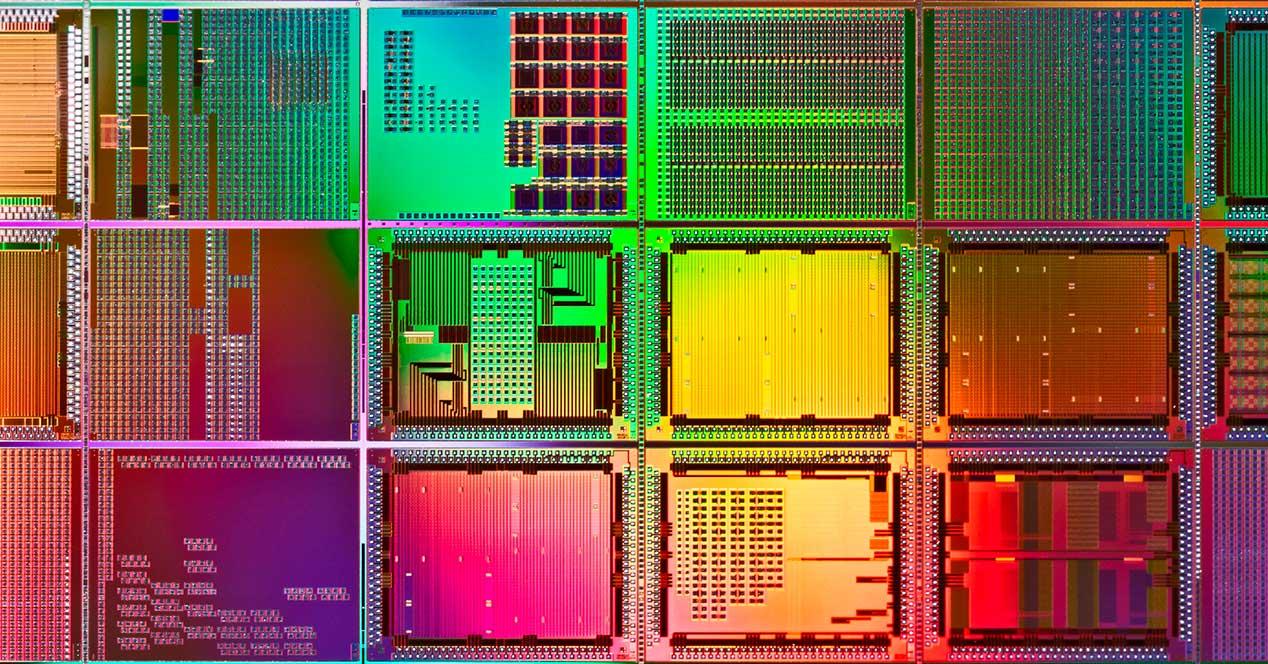

![]()

لا يوجد أعمى من لا يريد أن يرى. مثل هذا القول الذي يبدو أنه يكره قطاعات معينة من تصنيع الملكية الفكرية للشركات الكبيرة. يتم الاستثمار ويجب أن تكون الطريقة هي مشاركة سلسلة على الأقل من الواجهات القياسية لتكامل الشرائح ، وهو أمر من شأنه أن يضر بها اقتصاديًا بشكل خطير.

المثال التالي بسيط ، NVMe ، SATA SSDs أو DRAM نفسها. يستخدمون نفس الواجهة ، بحيث لا تحتاج الأجزاء المختلفة إلى معرفة تفاصيل الأجزاء الأخرى نظرًا لأنهم يعرفون ما يجب الالتزام به وكيف يجب أن يكون تصميم PCBs والاتصالات والرقائق.

إنها توفر التكاليف ، والوقت ، وتحسن الأرصدة المالية ، وتنتج أكثر وأفضل ، ولكن الأهم هو أن تتنافس جميع الشركات في نفس الظروف ، مما يعزز القدرة التنافسية للقطاع.

في هذا الصدد ، وكيف يمكن أن يكون الأمر خلاف ذلك في مواجهة مثل هذه الفوضى ، تقوم الشركات الكبيرة بتطوير أساس هذه المعايير التي تشتد الحاجة إليها ، وتقنيات التوصيل البيني مع واجهات مفتوحة للشركات للانضمام إلى قضيتها.

لدرجة أن النزاع حاليًا سيكون بين أربعة متنافسين على اللقب: AIB و BoW و OpenHBI و XRS حيث بالإضافة إلى ذلك ODSA تتطور من جانبها ما يسمى ب تبادل تصميم Chiplet أو CDX ، شكل مفتوح للتبادل الآمن للمعلومات يحافظ على السرية ويحافظ على سير العمل والمعلومات للنماذج الأولية.

مع وضعه في الاعتبار ، نحاول تنظيم الواجهات المختلفة للبدء في إنشاء نظام سري غير متجانس يصمم الشرائح الرقيقة تدريجيًا بسهولة أكبر واستنادًا إلى المعيار الذي ينتهي به الأمر. قد يكون هناك حالة عدم وجود فائز واحد ، لأن الصناعة تحتاج إلى الابتكار بطريقتين على الأقل ، ولكن على الأقل ستكون الخطوة الأولى للوصول إلى هدف مشترك للجميع.

يتطلب إنشاء الرقائق وترابطها أيضًا توحيد المعايير

إذا كان من الصعب بالفعل حل اللغز ، ضع في اعتبارك أن تصميمات الترابط (المعروفة أيضًا بالنتوءات أو النتوءات الدقيقة) لم يتم تعريفها أيضًا على أنها قياسية. تقوم كل شركة بإنشاء المطبات والعبوات الخاصة بها ، لذلك نظرًا لعدم وجود توحيد في هذا الأمر ، هناك حاجة إلى أدوات محددة للتحقق ، وإنشاء والإشراف على الرقاقات ، سواء للرقائق أو للمدخلات.

الخطوات كلها تقريبًا مؤتمتة ، حيث تمر الرقائق عدة ساعات من الاختبار والاختبار والمراقبة بالمحتوى الكهربائي والفيزيائي والمرئي. كما هو متوقع ، يربط استخدام قشريات دقيقة هي أكبر بكثير في الحجم المادي في شيبليت منها في يموت متجانسة ، حيث يمكن أن تصل من 25 ميكرون إلى 40 ميكرون.

للحصول على فكرة ، وأخذ رقاقة 300 ملم ، فإن فحص كل اتصال من الميكروبات هو مثل تحديد رأس دبوس في ملعب لكرة القدم ، وفقًا لنائب رئيس FormFactor. الدقة لا تصدق وهذا يعني أنه بدون معيار ستستمر التكاليف في النمو للجميع ، حيث تقترب منه الميكروبات الجديدة 10 ميكرومتر ، ولن تتوقف الاختبارات عن الارتفاع في السعر بسبب الدقة الهائلة التي يحتاجونها للاختبارات المقابلة.

إذن ، وباختصار ، هل هي ميزة أو عيب أن تتبع مسار الشرائح الصغيرة؟ من الجيد جدًا أن نرى البحر من الشاطئ ونتأثر بكل عملية إطلاق أو تقنية مصممة من قبل Intel و AMD. لكن القطاع تحت الماء ليس واضحًا تمامًا ، وعلى الرغم من تحديد الخطوات التي يجب اتباعها ، فإن خطوات Swan على سبيل المثال لن تترك وحدات المعالجة المركزية المتجانسة جانبًا حتى تتمكن الصناعة بأكملها من اتباع سلسلة من المعايير.

سيتعين على AMD تحمل ثقل كل ما قيل ، وفي أيدي شركة TSMC ، حيث علقنا بالفعل أكثر من مرة ، يجب أن ترتفع أسعار معالجاتها عاجلاً أو آجلاً لتبقى مربحة وقبل كل شيء ، تزيد من هامش الربح. لن يكون كمنعم رحلة لأحد العملاقين ، وقد إنتل EMIB و Foveros و AIB و Co-EMIB ، TSMC قيد التطوير مع نظام الرقاقة المتكاملة (SoIC) وتحاول AMD تربيع القطع من أجل بنيتها الجديدة القائمة على الشركات المختلفة التي تزود ما هو ضروري لهذه الشرائح.

إذا كان أي شخص يعتقد أن هذا هو الخياطة والغناء ، كانوا مخطئين للغاية. إن المستقبل ليس أسود ، ولكنه يتطلب صفقات وخسائر طويلة المدى يتحملها الجميع.